### 12.1 OVERVIEW

This chapter describes several hardware interface solutions for connecting ADSP-2100 Family digital signal processors to peripheral devices, such as codecs. Because the peripheral devices are also programmable, this chapter includes the code for configuring these devices. The corresponding subroutines are listed at the end of each section.

This chapter includes the following hardware interface solutions:

- ADSP-2105/AD1849 SoundPort®

- ADSP-2111/AD1849 SoundPort

- ADSP-2101/AD1847 SoundPort

- ADSP-2100 Family/DRAM Interfacing

- Loading an ADSP-2101 Program Through the Serial Port

- Memory Interfacing with the ADSP-2105

Although most sections of this chapter contain solutions for specific ADSP-2100 Family processor hardware interfaces, the code listings can be modified to accommodate additional solutions. Several sections also include suggestions for modifying the code.

When you change the code to accommodate ADSP-2100 Family DSPs other than the ones specified, you must consider differences in interrupt vectors, chip architecture, peripheral devices, and memory configurations.

### 12.2 SOUNDPORT INTERFACES

This section contains three solutions for interfacing the ADSP-2100 Family DSPs with AD1849 and AD1847 SoundPorts.

### 12.2.1 ADSP-2111/AD1849 SoundPort Interface

This code in this section provides the initialization of the control functions needed to connect the AD1849 SoundPort Stereo Codec to the ADSP-2111. Listing 12.1 performs an ADSP-2111/AD1849 talk-through routine.

You should consider the following points when using this program:

- The AD1849 works on 64-bit words. The DSP sees this as four 16-bit words. Be careful when you set up control words so that the appropriate control bits are in the correct locations.

- The source of SPORT signals is different between data and control modes. In *control mode*, the DSP is expected to provide all signals. In *data mode*, the AD1849 provides the signals. You must reset the DSP SPORT when you change from control mode to data mode.

- When you change sampling rates (or other system parameters), you

must change the appropriate control field in the command word and in

the mask word used to check DCB status. Also, remember that the

AD1849 initiates its auto calibration sequence once the sampling rate is

changed.

- If you retain indirect addressing into the receive and transmit autobuffers, the I3 pointer must be set immediately after the code enters the interrupt routine. A delay can cause pointer misalignment and render the code inoperable.

The following suggestions are included for modifying the code:

- Direct Addressing: Instead of resetting an indirect pointer into the receive and transmit buffers, try using direct addressing. For example, *dm(datain)* is the left channel data, *dm(datain+1)* is the right channel data.

- Transmit Interrupt: Because of interrupt timing and other system constraints, it may be advantageous to time your system from the transmit interrupt instead of the receive interrupt. Refer to the *ADSP-2100 Family User's Manual* for more information about the different interrupt latencies that are inherent with the different approaches.

```

ADSP-2111 - AD1849(SOUNDPORT) INTERFACE PROGRAM

Analog Devices Sept, 1991

This program is written to run on an ADSP-2111. However, it can be easily

changed to work with an ADSP-2101 by modifying the interrupt vector table.

For the hardware connections between the ADSP-2111 and AD1849 please refer to

the diagrams shown on the AD1849 data sheet.

The AD1849 will be set up as follows:

(NC indicates a no care state, all control reg are 1 bit unless indicated

by [#bits])

Control time slot control bits:

DCB=0 followed by 1

autocalibrate

AC=1

DFR=5

Data conversion frequency, 44.1kH [3]

ST=1

stereo mode

DF=0 dataformat is 16 bit twos complement [2]

MCK=2 16.9344 MHz is the master clock [2]

FSEL=0 frame size, 64 bits [2]

MS=1 master mode (i.e. receive external serial clock)

TXDIS=0 enable serial output

ENL=0 disable loopback testing

loopback mode analog/digital (disabled) paralell I/O bits not used [2]

ADL=NC

PIO=NC

REVID=NC

Data Timeslot Control Bits:

OM0=1 enable line 0 output

OM1=1

enable line 1 output

OMI=I enable line I output

LO=O no attenuation of left channel output [6]

SM=O mono output is muted

RO=O no attenuation of right channel output [6]

PIO=NC paralell I/O bits not used [2]

OVR=NC overrange INPUT

IS=O line-level stereo input selected

IS=0

line-level stereo input selected

no gain for left channel [4]

LG=0

no monitor mix (i.e. ADC output is not mixed with DAC input

MA=15

no gain for right channel [4]

******************

This program makes use of the multi-channel mode that is available on the

```

SPORTO and it also uses autobuffering to reduce interrupt service overhead. For a description of the multi-channel and autobuffering features, please refer to the ADSP-2111 or ADSP-2101 architecture user's manuals.

(listing continues on next page)

In its current condition, this program can be used "as is" to perform straight talkthrough (at 44.1 KHz sample rate) on both left and right channels of the AD1849. The incoming audio data from the 16bit ADCs is placed in a short buffer and immediately sent out to the 16bit DACs.

The initial setup and handshaking with the AD1849 starts with the "START" routine. A state machine to perform the handshaking is executed in software. Once the AD1849 is configured properly, the processor enters the WAIT\_DATA loop and waits for serial port interrupt requests.

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

This program is booted into the ADSP-2111 on power-up.

```

.MODULE/ABS=0/BOOT=0

AD1849;

.VAR/CIRC CTRLIN[4];

{circular buffers for data input and}

.VAR/CIRC CTRLOUT[4];

{output for data mode and control mode}

.VAR/CIRC DATAIN[4];

.VAR/CIRC DATAOUT[8];

FIRST_FLG;

DCB_FLG;

.VAR

.VAR

.VAR

DMODE FLG;

{restart interrupt}

JUMP START;nop;nop;nop;

{IRQ2 int, not used}

RTI;nop;nop;nop;

{HIP write int, not used}

RTI; nop; nop; nop;

{HIP read int, not used}

RTI;nop;nop;nop;

JUMP SETUPCONTROL;nop;nop;

{SPORTO transmit int}

{SPORTO receive int}

JUMP NEWDATA;nop;nop;

{SPORT1 tx or IRQ1 int, not used}

RTI; nop; nop; nop;

{SPORT1 rx or IRQ0 int, not used}

RTI;nop;nop;nop;

{timer int, not used}

nop;nop;nop;

START:

RESET FL0;

{set the AD1849 D/C pin low}

L0=%CTRLIN;

M0 = 1;

I0=^CTRLIN;

L1=%CTRLOUT;

M1=1;

I1=^CTRLOUT;

AX0=1;

DM(FIRST_FLG) = AX0;

DM(DCB_FLG) = AX0;

AX0=0;

DM(DMODE_FLG) = AX0;

AY0=B#0010000100101100;

```

```

{Initialize contol mode output buffer}

DM(I1,M1) = B#0010000100101100;

{DCB=0,AC=1,DFR=05,ST=1,DF=00}

DM(I1,M1) = B#001000100000000;

{MCK=02,FSEL=0,MS=0,TXDIS=0}

{ENL=0,ADL=0}

DM(I1,M1) = B#0000000000000000;

\{PIO = 00\}

DM(I1,M1) = B#0000000000000000;

{REVID=NC}

L2 = 0;

{linear addressing for register }

I2 = 0x3fef;

{pt. to last DM cntrl req}

{3FEF}

DM(I2,M1) = 0x0000;

{sport1 not used}

3FF0}

DM(I2,M1) = 0x0000;

DM(I2,M1) = 0x0000;

3FF1 }

3FF2}

DM(I2,M1) = 0x0000;

{3FF3}

DM(I2,M1) = 0X0283;

{autobuf. rx:i0, m0 tx:i1,m1}

{3FF4}

DM(I2,M1) = 383;

{sport rfsdiv, sets up FRAME sync freq}

{3FF5}

DM(I2,M1) = 849;

sport0 sclkdiv, SCLK will be less than}

{8KHz from control mode}

{3FF6}

DM(I2,M1) = B#1100010100011111;

{sport0 control register:

multi-channel mode, 24 channels

internal sclk & rfs

normal framing mode

frame sync not inverted

16 bit word length}

DM(I2,M1) = 0x000F;

{3FF7}

{first 4 xmit multichannels used}

3FF8}

DM(I2,M1) = 0x0000;

3FF9 }

DM(I2,M1) = 0x000F;

{first 4 rx multichannels used}

{3FFA}

DM(I2,M1) = 0x0000;

DM(I2,M1) = 0x0000;

{TSCALE register}

{3FFB}

DM(I2,M1) = 0x0000;

{TCOUNT register}

3FFC}

{3FFD}

DM(I2,M1) = 0x0000;

{TPERIOD register, initializing value

for TCOUNT after every interrupt}

{3FFE}

DM(I2,M1) = 0x0000;

{external data memory waits=0}

ICNTL=0x00;

IMASK=B#00010000;

{only SPORT transmit intrpt enabled

initially while in control mode}

{send first 16bits of ctrl word}

AX0=DM(I1,M1);

TX0=AX0;

{3FFF}

DM(I2,M1) = 0x1418;

{system control reg: sport0 enabled}

```

```

{Wait for an interrupt indicating that transmit register is ready for

new data and that the 2111 has received a 16bit word}

WAIT1:

AX1=DM(DMODE FLG);

AR=PASS AX1;

IF GT JUMP GO_DMODE;

JUMP WAIT1;

SETUPCONTROL:

AX0=DM(FIRST FLG);

AF=PASS AX0;

IF NE JUMP DECR_FIRST;

AX0=DM(DCB FLG);

AR=PASS AX0;

IF EQ JUMP DCBFLG_SET;

AX0=DM(CTRLIN);

{DCB FLG has not been set yet}

AR=AX0 XOR AY0;

{check all incoming bits including DCB bit}

{set flag if DCB was 0}

IF EQ JUMP SET_DCB;

RTI;

DCBFLG SET:

AX0=DM(CTRLIN);

{DCB_FLG was set}

{only check for DCB bit}

AR=AX0 AND AY0;

IF NE JUMP SETDMODE;

{if DBC=1 ready for datamode}

RTI;

SET_DCB: AX0=0;

DM(DCB FLG)=AX0;

AX0=B#0010010100101100;

{DCB was 0, prepare to send DCB=1}

DM(CTRLOUT) = AX0;

AY0=B#000001000000000;

RTI;

DECR_FIRST:

AX0=0;

DM(FIRST_FLG) = AX0;

RTI;

SETDMODE:

IMASK=0;

{disable sport0}

AX0=0X0818;

DM(0X3FFF) = AX0;

{ At this point we could boot page#1 and do the following data mode setup

after the reboot occurs. This would free up some PM RAM for other uses}

I1 = ^DATAOUT;

DM(I1,M1) = 0x0000;

{reset output & input data buffers}

DM(I1,M1) = 0x0000;

{initialize embedded control bits}

DM(I1,M1) = B#000000011110000;

{PIO=00,OVR=1,IS=0,LG=0,MA=15,RG=0}

```

```

DM(I1,M1) = 0x0000;

DM(I1,M1) = 0x0000;

{reset output & input data buffers}

{initialize embedded control bits}

DM(I1,M1) = B#110000000000000000; \{OM1=1,OM1=1,LO=0,SM=1,RO=0\}

DM(I1,M1) = B#000000011110000; {PIO=00,OVR=1,IS=0,LG=0,MA=15,RG=0}

AX0=0X861F;

DM(0X3FF6) = AX0;

{sport0 control:

multi-channel mode

external sclk & rfs

32 word frames, 16bit words}

SET FL0;

{set D/C high}

AX0=1;

DM(DMODE FLG) = AX0;

RTT;

GO DMODE:

L0=%DATAIN;

TO = ^DATATN;

L1=%DATAOUT;

I1=^DATAOUT;

M2 = 3;

L3 = L1;

AX0=0XFFFF;

{enable all multi-channel words}

DM(0X3FF7) = AX0;

DM(0X3FF8)=AX0;

DM(0X3FF9) = AX0;

DM(0X3FFA) = AX0;

{send first 16bits of data}

AX0=DM(I1,M1);

TX0=AX0;

AX0 = 0X1418;

{turn on sport0}

DM(0X3FFF) = AX0;

IFC=B#000000111111;

{clear all pending interrupts}

IMASK=B#00001000;

{sport0 rx interrupt on}

WAIT_DATA:

JUMP WAIT DATA;

{wait for sport0 rx autobuffer interrupt}

NEWDATA:

I3=I1;

MODIFY(I3,M2);

{this routine sends the incoming}

AX0=DM(DATAIN);

{a/d data straight to the d/a by}

DM(I3,M1)=AX0;

AX0=DM(DATAIN+1);

{copying newly arrived data words from}

DM(I3,M1)=AX0;

{DATAIN into the DATAOUT buffer}

RTI;

{The DATAOUT buffer is twice as long as the DATAIN buffer, since it contains}

\{control\ words, as well as output data. This program ignores the control\}

\{ \mathtt{words} \ \mathtt{arriving} \ \mathtt{back} \ \mathtt{from} \ \mathtt{the} \ \mathtt{AD1849} \ \mathtt{during} \ \mathtt{the} \ \mathtt{data} \ \mathtt{mode} \}

.ENDMOD;

```

### 12.2.2 ADSP-2105/AD1849 SoundPort Interface

This section contains a program that provides the initialization of control functions needed to interface the AD1849 SoundPort Stereo Codec to the ADSP-2105. Listing 12.2 is an ADSP-2105/AD1849 talk-through routine: incoming data is echoed immediately to the output.

You should consider the following points when using this program:

- Multichannel mode is not available on SPORT1, so SPORT1 is run in unframed mode. Any disruption in the serial data stream can cause the AD1849 to lose synchronization. The interface code checks incoming control words, and if there is a discrepancy, the code resets SPORT1. This could cause a loss of data if the data stream is corrupted. In a stable, electrically clean environment you should not have any significant problems. The SPORT receive interrupt routine checks for errors, and this routine can be removed if your environment does not require it.

- Control for the AD1849's D/C line is derived from a latched external memory-mapped port (the *mode\_sel* port definition). The program uses data bit D8 (the LSB) as the mode select flag.

- RFS1 and TFS1 must be tied together for codec initialization and operation.

```

ADSP-2105 - AD1849 (SOUNDPORT) INTERFACE PROGRAM

Analog Devices Jan, 1992

Revised 12/10/92: Equal length Tx and Rx buffers. Direct addressing

for Tx autobuffer writes (NEWDATA routine)

This program is written to run on an ADSP-2105.

For the hardware connections between the ADSP-2105 and AD1849, please refer to

the diagrams shown on the AD1849 data sheet.

Note: RFS1 and TFS1 MUST be tied together in order to initialize and operate

the codec.

The AD1849 will be set up as follows:

(NC indicates a no care state, all control reg are 1 bit unless indicated

by [#bits])

Control time slot control bits:

DCB=0 followed by 1

AC=1

autocalibrate

DFR=5

Data conversion frequency, 44.1kH [3]

stereo mode

ST=1

dataformat is 16 bit twos complement [2]

DF = 0

DF=0 dataformat is to bit twos complement [2]

MCK=2 16.9344 MHz is the master clock [2]

FSEL=0 frame size, 64 bits [2]

MS=1 master mode (i.e. receive external serial clock)

TXDIS=0 enable serial output

ENL=0 disable loopback testing

ADL=NC loopback mode analog/digital (disabled)

PTO=NC parallel I/O bits not used [2]

parallel I/O bits not used [2]

REVID=NC

Data Timeslot Control Bits:

OM0=1 enable line 0 output

enable line 1 output

no attenuation of left channel output [6]

OM1=1

LO=0

mono output is muted

SM=0

no attenuation of right channel output [6]

RO=0

parallel I/O bits not used [2]

PIO=NC

OVR=NC

overrange INPUT

line-level stereo input selected

TS=0

no gain for left channel [4]

LG=0

MA=15 no monitor mix (i.e. ADC output is not mixed with DAC input)

no gain for right channel [4]

*********************

```

(listing continues on next page)

In its current condition, this program can be used "as is" to perform straight talkthrough (at 44.1 KHz sample rate) on both left and right channels of the AD1849. The incoming audio data from the 16bit ADCs is placed in a short buffer and immediately sent out to the 16bit DACs.

The initial setup and handshaking with the AD1849 starts with the "START" routine. A state machine to perform the handshaking is executed in software. Once the AD1849 is configured properly, the processor enters the WAIT\_DATA loop and waits for serial port interrupt requests.

This program is booted into the ADSP-2105 on power-up.

```

************************************

MODULE/ABS=0/BOOT=0 AD1849;

.VAR/CIRC CTRLIN[4];

{circular buffers for data input and}

.VAR/CIRC CTRLOUT[4];

{output for data mode and control mode}

.VAR/CIRC DATAIN[4];

.VAR/CIRC DATAOUT[4];

FIRST_FLG;

DCB_FLG;

DMODE_FLG;

sync_flag;

.VAR

.VAR

.VAR

.var

.port mode_sel;

{latched control for Control/Data line}

JUMP START;nop;nop;

{restart interrupt}

RTI; nop; nop; nop;

{IRQ2 int, not used}

RTI;nop;nop;nop;

{SPORT0 tx not used}

{SPORT0 rx not used}

RTI;nop;nop;nop;

JUMP SETUPCONTROL;nop;nop;nop; {SPORT1 transmit int}

JUMP NEWDATA; nop; nop;

{SPORT1 receive int}

{timer int, not used}

RTI;nop;nop;nop;

START:

AX0=0;

dm(mode sel)=AX0;

{set AD1849 D/C pin low}

L0=%CTRLIN;

M0=1;

I0=^CTRLIN;

L1=%CTRLOUT;

M1=1;

I1=^CTRLOUT;

DM(FIRST_FLG) = AX0;

DM(DCB FLG) = AX0;

AX0=0;

{in control mode}

DM(DMODE_FLG) = AX0;

AY0=B#0010000100101100;

```

```

{Initialize contol mode output buffer}

DM(I1,M1) = B#0010000100101100;

{DCB=0,AC=1,DFR=05,ST=1,DF=00}

{MCK=02,FSEL=0,MS=1,TXDIS=0}

DM(I1,M1) = B#0010001000000000;

{ENL=0,ADL=0}

DM(I1,M1) = B#000000000000000;

{PIO = 00}

DM(I1,M1) = B#000000000000000;

{REVID=NC}

L2 = 0;

{linear addressing for register}

I2 = 0x3fef;

{point to last DM cntrl req}

{sport1 autobuffer register}

{3FEF}

DM(I2,M1) = 0x0283;

DM(I2,M1) = 383;

{3FF0}

{rfsdiv1, not really used}

{3FF1}

DM(I2,M1) = 849;

{sclkdiv1}

{3FF2}

DM(I2,M1) = B\#0100000100011111; {sport1 control register:

internal sclk & rfs

normal framing mode

frame sync not inverted

16-bit word length

I2=0x3ffb;

{3FFB}

DM(I2,M1) = 0x0000;

{TSCALE register}

DM(I2,M1) = 0x0000;

{TCOUNT register}

{3FFC}

{TPERIOD register, initializing value

\{3FFD\} DM(I2,M1) = 0x0000;

for TCOUNT after every interrupt }

\{3FFE\} DM(I2,M1) = 0x0000;

{external data memory waits=0}

ICNTL=0x00;

IMASK=B#000100;

{only SPORT1 tx interurpt enabled

initially while in control mode }

{.... Set bit test mask for DCB bit, used in tx interrupt state machine ....}

AY0=B#0010000100101100; {test mask for DCB bit}

send first control word to switch codec to data mode

AX0=DM(I1,M1);

{send first 16bits of ctrl word}

TX1=AX0;

{3FFF}

DM(I2,M1) = 0x0c18;

{system control req: sport1 enabled}

{.... Wait for an interrupt indicating that transmit register is ready for

new data and that the 2105 has received a 16bit word

WAIT1:

{check dmode flag}

AX1=DM(DMODE_FLG);

AR=PASS AX1;

IF GT JUMP GO_DMODE;

{if set, in data mode}

{else, wait for initialization to

JUMP WAIT1;

be completed from tx interrupt

routine

GO DMODE: L0=%DATAIN;

{init I0, L0 for rx autobuffer}

I0=^DATAIN;

{init I1, L1 for tx autobuffer}

L1=%DATAOUT;

I1=^DATAOUT;

```

(listing continues on next page)

```

M2 = 3;

AX0=DM(I1,M1);

{send first 16bits of data}

TX1=AX0;

AX0=0X0c18;

DM(0X3FFF) = AX0;

{turn on sport1}

IFC=B#00000111111;

{clear all pending interrupts}

{cycle for IFC latency}

IMASK=B#000010;

{sport1 rx interrupt on}

WAIT DATA:

{wait for sport1 rx autobuffer interrupt}

JUMP WAIT DATA;

{sport1 tx interrupt routine}

{This routine initializes the AD1849 control mode and then waits to

see if the codec is ready to be switched to data mode. The routine

also initializes the transmit autobuffer with the appropriate

data-mode control words. See the AD1849 data sheet for a complete

explanation of control word bits.

\{ \mathtt{Note} \colon \mathtt{AYO} \ \mathtt{contains} \ \mathtt{a} \ \mathtt{bit} \ \mathtt{mask} \ \mathtt{and} \ \mathtt{must} \ \mathtt{NOT} \ \mathtt{be} \ \mathtt{modified} \ \mathtt{elsewhere}

SETUPCONTROL:

{first time through?}

AX0=DM(FIRST FLG);

AF=PASS AX0;

IF NE JUMP DECR FIRST;

{if so, wait until next word transmitted}

AX0=DM(DCB_FLG);

AR=PASS AX0;

IF EQ JUMP DCBFLG_SET;

AX0=DM(CTRLIN);

{DCB_FLG has not been set yet}

AR=AX0 XOR AY0;

{check all incoming bits including DCB bit}

IF EQ JUMP SET DCB;

{set flag if DCB was 0}

DCBFLG_SET:

{DCB_FLG was set}

AX0=DM(CTRLIN);

{only check for DCB bit}

AR=AX0 AND AY0;

{if DBC=1 ready for datamode}

IF NE JUMP SETDMODE;

RTI

SET DCB:

AX0=0;

DM(DCB_FLG) = AX0;

AX0=B#0010010100101100;

{DCB was 0, prepare to send DCB=1}

DM(CTRLOUT) = AX0;

AY0=B#000001000000000;

RTI;

```

```

DECR FIRST: AX0=0;

DM(FIRST_FLG) = AX0;

{if first time, set flag=0}

RTI;

SETDMODE:

IMASK=0;

{disable sport1}

AX0 = 0X0418;

DM(0X3FFF) = AX0;

{ At this point we could boot page#1 and do the following data mode setup

after the reboot occurs. This would free up some PM RAM for other uses.

The data mode setup initializes the transmit autobuffer control word

elements. These values are not changed in this talkthrough application.

I1 = ^DATAOUT;

L1=0;

DM(I1,M1) = 0x0000;

{reset output & input data buffers}

DM(I1,M1) = 0x0000;

{initialize embedded control bits}

DM(I1,M1) = B#110000000000000;

{OM1=1,OM1=1,LO=0,SM=0,RO=0}

DM(I1,M1) = B#000000011110000;

{PIO=00,OVR=0,IS=0,LG=0,MA=15,RG=0}

DM(I1,M1) = 0x0000;

{reset output & input data buffers}

DM(I1,M1) = 0x0000;

{initialize embedded control bits}

DM(I1,M1) = B#000000011110000; {PIO=00,OVR=0,IS=0,LG=0,MA=15,RG=0}

AX0=0X001F;

DM(0X3FF2) = AX0;

{ sport1 control:}

internal tfs

external sclk & rfs

16bit words }

AX0=1;

dm(mode sel)=AX0;

{set D/C high}

DM(DMODE FLG) = AX0;

{set data mode flag high}

RTI;

}

sport1 rx interrupt routine

This routine sends the incoming a/d data straight to the d/a by copying

newly arrived data words from the DATAIN buffer into the DATAOUT buffer

NEWDATA: AX0=DM(DATAIN);

{get LEFT channel data}

DM(dataout)=AX0;

{output LEFT channel data}

AX0=DM(DATAIN+1);

{get RIGHT channel data}

DM(dataout+1)=AX0;

{output RIGHT channel data}

```

(listing continues on next page)

```

Error checking section (optional). Incoming control words are compared

to the outgoing control words.

{read known output control word}

ax0=dm(dataout+2);

ay0=dm(datain+2);

{read newly received control word}

ar=ax0-ay0;

{compare, they should be the same}

if eq jump no_error;

{if same, no error}

ax0=dm(sync_flag);

{if not, read SYNC FLAG}

ar=pass ax0;

{test for 0 or 1}

{if 1, second failure, reset SPORT1}

if ne jump reset_sport;

ar=pass 1;

{else, first failure, set SYNC_FLAG}

dm(sync_flag)=ar;

{return}

reset sport:

si=0x418;

{disable SPORT1}

dm(0x3fff)=si;

{re-enable SPORT1}

si=0xc18;

dm(0x3fff)=si;

no_error:

ar=pass 0;

{reset SYNC FLAG}

dm(sync_flag)=ar;

{return}

The DATAOUT buffer is twice as long as the DATAIN buffer, since it

contains control words, as well as output data. This program ignores the

\{ control words arriving back from the AD1849 during the data mode, except

for the purpose of error checking.

ax0=dm(0x3fff);

next:

ay0=b#0000001001000000;

ar=ax0 OR ay0;

dm(0x3fff)=ar;

rti;

.ENDMOD;

```

Listing 12.2 ADSP-2105/AD1849 Talk-Through Routine (18492105.DSP)

### 12.2.3 ADSP-2101/AD1847 SoundPort Interface

This section contains a program that provides the initialization of control functions needed to interface the AD1847 SoundPort Stereo Codec to the ADSP-2101.

The AD1847 has a TDM serial interface. The code provided should work without modifications for the ADSP-2101, ADSP-2103, and ADSP-2115. The code requires minor modifications to the interrupt vector table to use it with the ADSP-2111, ADSP-2171, and ADSP-21msp5x processors. Also, you can probably use the additional flags available on these processors to optimize the code.

Analog Devices does not recommend using this code on the ADSP-2105 because the ADSP-2105 does not have a TDM serial port. For additional information about AD1847 interfacing, refer to the "README" file included with the other files for this chapter.

Listing 12.3 is an ADSP-2101/AD1847 talk-through routine.

You should consider the following points when using this program:

- Although the AD1847 and the ADSP-2101 are set for 32-word blocks, the AD1847 works on 16-word cycles. Therefore, control words are sent on time slots 0 and 16, left channel data is sent on slots 1 and 17, and right channel data is sent on slots 2 and 18. Receive data follows a similar pattern.

- The AD1847 has a two-sample buffer to allow for slower sampling rates. Since the AD1847's serial bit clock rate is fixed, the interval between time slot 0 and time slot 16 is less than the sample period. For example, for an 8 kHz sampling rate, data is expected every 125 μsec. At that sampling rate, the serial bit clock produced by the AD1847 is 12.288 MHz, yielding a time span between data samples of 20.83 μsec (81.38 ns x 16 bits/word x 16 words). The actual data received, however, is sampled at the correct time interval and stored in the AD1847's output buffer. Remember that time is needed to convert the data, and that the AD1847 can wait between generating frame syncs to insure proper sample timing.

.module/ram/abs=0 ad1847; /\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\* ADSP-2101 -> AD1847: Talkthru Interface This code provides the necessary initializations and setup to allow for communication between the AD1847 SoundPort codec and the ADSP-2100 family Serial Port 0. This interface code was written around an AD1847 connected to an ADSP-2101 EZ-Lab board through the J2 SPORT Connector. When the board is RESET, the codec is initialized for an 8kHz sampling rate of stereo PCM data. This module can be used without modification for the ADSP-2101, ADSP-2103, and ADSP-2115. Use with the ADSP-2111, ADSP-2171, or ADSP-21msp5x processors would require modification of the interrupt vector table and any instructions relating to IFC, IMASK, or any other interrupt-related structure. This interface is not recommended for the ADSP-2105. \*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\* 0xc000, 0x0000, 0x0000; /\* Initially set MCE .init tx buf: .var/dm/ram/circ init cmds[13]; /\* Initial codec setup: /\* 0: Left Input Control: 0 gain, Line 1 input /\* 1: Right Input Control: 0 gain, Line 1 input /\* 1. August /\* 2: Left Aux #1 Input Control: Muted /\* 3: Right Aux #1 Input Control: Muted #2 Input Control: Muted \* / \* / /\* 5: Right Aux #2 Input Control: Muted /\* 6: Left DAC Control: 0 attenuation, muted /\* 7: Right DAC Control: 0 attenuation, muted /\* 8: Data Format: XTAL1, 8kHz sampling, stereo, 16-bit linear PCM /\* 9: Interface Config: Playback enabled, ACAL allowed /\* 10: Pin Control: CLKOUT active, XCTL1/0 LO /\* 12: Misc. Info: Transmit on 0,1,2, 32-word frame /\* 13: Digital Mix Control: DME Disabled, 0 attenuation \* / /\* To start-up the codec with any other properties, /\* change the appropriate initialization value. /\* Refer to the AD1847 data sheet for detailed register /\* descriptions. /\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

```

.init init cmds:

0xc000,

0xc100,

0xc280,

0xc380,

0xc480,

0xc580,

0xc680,

0xc780,

0xc850,

0xc909,

0xca00,

0xcc40,

0xcd00;

.var/dm

stat_flag;

reset_vect: jump sys_init; nop; nop; nop;

irq2_svc:

rti; nop; nop; nop;

tx0_irq:

ar = dm(stat_flag);

ar = pass ar;

if eq rti;

jump next_cmd;

rx0_irq:

jump input_samples;

rti; nop; nop;

rti; nop; nop; nop;

rti; nop; nop; nop;

rti; nop; nop; nop;

/******

Code Start:

*******

sys_init:

i0 = \text{rx\_buf};

10 = %rx_buf;

i1 = ^tx_buf;

11 = %tx_buf;

i3 = ^init_cmds;

13 = %init_cmds;

m1 = 1;

```

```

/********

sport0 setup:

multichannel enable, ext. sclk, MFD=1,

32 words, ext. rfs, DTYPE 00, 16 bits

********

ax0 = b#1000011000001111;

dm(0x3ff6) = ax0;

/******

Multichannel enable setup:

Rx: 3, 4, 5, 19, 20, 21

Tx: 0, 1, 2, 16, 17, 18

********

ax0 = b#000000000000111;

dm(0x3ff9) = ax0;

dm(0x3ffa) = ax0;

ax0 = b#000000000000111;

dm(0x3ff7) = ax0;

dm(0x3ff8) = ax0;

/*******

SPORT Autobuffer Setup

Rx: I0, M1

Tx: I1, M1

********

ax0 = b#0000001010000111;

dm(0x3ff3) = ax0;

ax0 = b#0001000000000000;

dm(0x3fff) = ax0;

/* SPORTO Enabled,

SPORT1 = FI, FO, IRQs */

start_setup:

ifc = b#0000001111111;

nop;

ax0 = 1;

dm(stat_flag) = ax0;

/* enable tx0 interrupt */

imask = b#010000;

ax0 = dm(i1, m1);

tx0 = ax0;

check_init:

/* wait for entire init */

ax0 = dm(stat_flag);

/* buffer to be sent to */

af = pass ax0;

if ne jump check_init;  /* the codec

check_aci:

/* once initialized, wait */

ax0 = dm(rx\_buf);

/* of autocalibration */

ar = ax0 and ay0;

if ne jump check aci;

```

```

idle;

ay0 = 0xbf3f;

ax0 = dm(init cmds+6);

ar = ax0 AND ay0;

dm(tx\_buf) = ar;

/* unmute left DAC */

idle;

ax0 = dm(init cmds+7);

ar = ax0 AND ay0;

dm(tx buf) = ar;

/* unmute right DAC */

idle;

ifc = b#000001111111;

imask = b#001000;

/* enable rx0 interrupt */

/*****************************

/* Main Loop: talkthru

talkthru:idle;

jump talkthru;

input_samples:

ena sec_reg;

/* L channel input */

ax1 = dm(rx\_buf+1);

/* R channel input */

mx1 = dm(rx buf+2);

dm(tx\_buf+2) = mx1;

dm(tx\_buf+1) = ax1;

rti;

next_cmd:

ena sec_reg;

ax0 = dm(i3,m1);

dm(tx\_buf) = ax0;

ax0 = i3;

ay0 = ^init_cmds;

ar = ax0 - ay0;

if gt rti;

ax0 = 0x8000;

dm(tx_buf) = ax0;

/* remove MCE if done initialization */

ax0 = 0;

.endmod;

```

Listing 12.3 ADSP-2101/AD1847 Talk-Through Routine (TALK\_47.DSP)

Listing 12.4 is an ADSP-2101/AD1847 demonstration routine. This program was written to demonstrate several features of the AD1847 when it is connected to the ADSP-2101 EZ-LAB® Demonstration Board.

This code provides the necessary initializations and setup to allow for communication between the AD1847 SoundPort codec and the ADSP-2100 family Serial Port 0.

This interface code was written around an AD1847 connected to an ADSP-2101 EZ-Lab board through the J2 SPORT Connector.

There are two modes of operation of this interface:

- 1) If the board is RESET, the codec is initialized for an 8kHz sampling rate of stereo PCM data.

- 2) If the FLAG\_IN button is held at reset, then the code enters its AD1847 configuration mode.

Codec attributes that can be changed are: line or microphone input source, input gain, and the sample rate. Do not press the IRQ2 button too fast when changing the sample rate as the codec needs time to perform its autoclibration procedure for each sampling rate.

#### Initialization:

SPORT1 must be configured as flags and interrupts. irq2 must be enabled.

Push <FLAGO> button to exit the setup routine

#### Operation:

Press and hold FLAG> button

Press and release <IRQ2> button

Release FLAG> button to enter the setup routine

Push <IRQ2> button to toggle between Line\_1 and Line\_2 input

Push <FLAG> button to go to the next state

Push <IRQ2> button to change the input gain, (8 levels)

Push <FLAG> button to go to the next state

Push <IRQ2> button to change the sample rate, (16 steps)

```

Line Input Gain Default: level 0 = 0dB

Sample Rates:

8 (default)

(1)

(9) 5.5125

16

(2)

(10) 11.025

(3)

27.42857

(11) 18.9

(12) 22.05

(4)

32

(13) 37.8

N/A

(5)

(14) 44.1

(6)

N/A

48

(7)

(15) 33.075

(8)

9.6

(16) 6.615

```

This module can be used without modification for the ADSP-2101, ADSP-2103, and ADSP-2115. Use with the ADSP-2111, ADSP-2171, or ADSP-21msp5x processors would require modification of the interrupt vector table and any instructions relating to IFC, IMASK, or any other interrupt-related structure.

```

This interface is not recommended for the ADSP-2105.

*******************************

.var/dm/ram/circ

rx buf[3];

.var/dm/ram/circ

.init tx_buf:

0xc000, 0x0000, 0x0000; /* Initially set MCE

.var/dm/ram/circ init_cmds[13]; /

Initial codec setup:

/* 0: Left Input Control: 0 gain, Line 1 input

* /

/* 1: Right Input Control: 0 gain, Line 1 input

* /

/* 2: Left Aux #1 Input Control: Muted

/* 3: Right Aux #1 Input Control: Muted

* /

/* 4: Left Aux #2 Input Control: Muted

/* 5: Right Aux #2 Input Control: Muted

* /

/* 6: Left DAC Control: 0 attenuation, muted

/* 7: Right DAC Control: 0 attenuation, muted

* /

/* 8: Data Format: XTAL1, 8kHz sampling, stereo,

* /

16-bit linear PCM

* /

/* 9: Interface Config: Playback enabled, ACAL allowed

* /

/* 10: Pin Control: CLKOUT active, XCTL1/0 LO

/* 12: Misc. Info: Transmit on 0,1,2, 32-word frame

* /

* /

/* 13: Digital Mix Control: DME Disabled, 0 attenuation

/***********************

```

```

.init init cmds:

0xc000,

0xc100,

0xc280,

0xc380,

0xc480,

0xc580,

0xc680,

0xc780,

0xc850,

0xc909,

0xca00,

0xcc40,

0xcd00;

.var/dm

stat_flag;

gain_state;

.var/dm

.var/dm

sampling_state;

.var/dm

chng_state;

reset_vect: jump setup_mode; nop; nop;

irq2_svc: toggle FLAG_OUT; si = 1; dm(chng_state) = si; rti;

tx0_irq:

ar = dm(stat_flag);

ar = pass ar;

if eq rti;

jump next_cmd;

rx0_irq:

jump input_samples;

rti; nop; nop;

rti; nop; nop; nop;

rti; nop; nop; nop;

rti; nop; nop; nop;

/*******

Code Start:

********

setup_mode:

set flag_out;

icntl = b#00100;

/* edge sensitive IRQ2 */

ax0 = 0x0018;

dm(0x3fff) = ax0;

nop;

nop;

if FLAG_IN jump sys_init;

ifc = b#000001111111;

ax0 = 0;

dm(chng_state) = ax0;

imask = b#100000;

```

```

wait_irq: ar = dm(chng_state);

/* wait for IRQ2 */

ar = pass ar;

if eq jump wait_irq;

imask = 0x0000;

wait_rel_FO:if NOT FLAG_IN jump wait_rel_FO; /* wait for FLAG_IN release */

ax0 = 0;

dm(chng_state) = ax0;

jump set codec;

sys_init:

i0 = ^rx buf;

10 = %rx_buf;

i1 = ^tx buf;

11 = %tx_buf;

i3 = ^init_cmds;

13 = %init cmds;

m1 = 1;

/********

sport0 setup: multichannel enable, ext. sclk, MFD=1,

32 words, ext. rfs, DTYPE 00, 16 bits

********

ax0 = b#1000011000001111;

dm(0x3ff6) = ax0;

/*******

Multichannel enable setup:

Rx: 3, 4, 5, 19, 20, 21

Tx: 0, 1, 2, 16, 17, 18

********

ax0 = b#000000000000111;

dm(0x3ff9) = ax0;

dm(0x3ffa) = ax0;

ax0 = b#000000000000111;

dm(0x3ff7) = ax0;

dm(0x3ff8) = ax0;

```

```

/*******

SPORT Autobuffer Setup

Rx: I0, M1

Tx: I1, M1

********

ax0 = b#0000001010000111;

dm(0x3ff3) = ax0;

ax0 = b#0001000000000000;

dm(0x3fff) = ax0;

/* SPORTO Enabled,

SPORT1 = FI, FO, IRQs */

start_setup:

ifc = b#000000111111;

nop;

ax0 = 1;

dm(stat_flag) = ax0;

imask = b#010000;

/* enable tx0 interrupt */

ax0 = dm(i1, m1);

tx0 = ax0;

check_init:

/* the codec */

if ne jump check_init;

check_aci:

ar = ax0 and ay0;

/* of autocalibration

if ne jump check_aci;

idle;

ay0 = 0xbf3f;

ax0 = dm(init\_cmds+6);

ar = ax0 AND ay0;

dm(tx\_buf) = ar;

/* unmute left DAC */

idle;

ax0 = dm(init cmds+7);

ar = ax0 AND ay0;

dm(tx\_buf) = ar;

/* unmute right DAC */

idle;

ifc = b#000000111111;

imask = b#001000;

/* enable rx0 interrupt */

```

```

/*****************************

/* Main Loop: talkthru

/*****************************

talkthru:

idle;

jump talkthru;

/****************************

input samples:

ena sec_reg;

/* L channel input */

ax1 = dm(rx buf+1);

mx1 = dm(rx\_buf+2);

/* R channel input */

dm(tx_buf+2) = mx1;

dm(tx buf+1) = ax1;

rti;

next cmd:

ena sec_reg;

ax0 = dm(i3, m1);

dm(tx\_buf) = ax0;

ax0 = i3;

ay0 = ^init_cmds;

ar = ax0 - ay0;

if qt rti;

ax0 = 0x8000;

dm(tx buf) = ax0;

ax0 = 0;

/* remove MCE if done initialization */

dm(stat_flag) = ax0;

/* reset status flag */

/******************************

Codec configuration section

************************

set_codec:

set FLAG_OUT;

ax0 = 0;

dm(gain\_state) = ax0;

dm(sampling\_state) = ax0;

IFC = b#0000001111111;

nop;

imask = b#100000;

/* enable IRQ2 interrupt */

```

(listing continues on next page)

```

Input Selection

*******

set_input:

if NOT FLAG_IN jump gain_wait;

sr0 = dm(chng_state);

af = pass sr0;

if eq jump set_input;

ax0 = dm(init cmds);

ay0 = 0xc080;

ar = ax0 XOR ay0;

/* if already set for line 1 in, */

if ne jump set_to_2;

/* switch to line 2

ax0 = 0xc000;

dm(init cmds) = ax0;

ax0 = 0xc100;

dm(init\_cmds+1) = ax0;

/* reset flag for IRQ2 */

ax0 = 0;

dm(chng_state) = ax0;

jump set_input;

set_to_2:

ax0 = 0xc080;

dm(init\_cmds) = ax0;

ax0 = 0xc180;

dm(init\_cmds+1) = ax0;

/* reset flag for IRQ2 */

ax0 = 0;

dm(chng_state) = ax0;

jump set_input;

/******

Gain Selection

*******

gain_wait:

if NOT FLAG_IN jump gain_wait; /* software switch de-bounce */

set_gain:

if NOT FLAG_IN jump sampling_wait;

sr0 = dm(chng_state);

af = pass sr0;

if eq jump set_gain;

ax1 = dm(gain_state);

ar = pass ax1;

if gt jump next1;

```

```

ax0 = 0xfff0;

/* set gain = 0 for both inputs */

ay0 = dm(init_cmds);

ar = ax0 AND ay0;

dm(init cmds) = ar;

ay0 = dm(init\_cmds+1);

ar = ax0 AND ay0;

dm(init\_cmds+1) = ar;

ax0 = 1;

dm(gain_state) = ax0;

jump set_gain;

next1:

ax1 = dm(gain_state);

ay0 = 1;

ar = ax1 - ay0;

if gt jump next2;

ax0 = 0x0002;

/* set gain = 2 = 3dB */

call gain_adjust;

jump set_gain;

next2:

ax1 = dm(gain_state);

ay0 = 2;

ar = ax1 - ay0;

if gt jump next3;

ax0 = 0x0006;

/* set gain = 4 = 6dB */

call gain_adjust;

jump set_gain;

next3:

ax1 = dm(gain_state);

ay0 = 3;

ar = ax1 - ay0;

if gt jump next4;

/* set gain = 6 = 9dB */

ax0 = 0x0002;

call gain_adjust;

jump set_gain;

next4:

ax1 = dm(gain_state);

ay0 = 4;

ar = ax1 - ay0;

if gt jump next5;

ax0 = 0x000e;

/* set gain = 8 = 12dB */

call gain_adjust;

jump set_gain;

```

(listing continues on next page)

```

next5: ax1 = dm(gain_state);

ay0 = 5;

ar = ax1 - ay0;

if gt jump next6;

ax0 = 0x0002;

/* set gain = 10 = 15dB */

call gain_adjust;

jump set_gain;

next6: ax1 = dm(gain_state);

ay0 = 6;

ar = ax1 - ay0;

if gt jump next7;

ax0 = 0x0006;

/* set gain = 12 = 18dB */

call gain adjust;

jump set_gain;

next7:

ax0 = 0x0002;

/* set gain = 13 = 21dB */

call gain_adjust;

ax0 = 0;

dm(gain_state) = ax0;

jump set_gain;

gain adjust

* /

gain_adjust:

ay0 = dm(init_cmds);

ar = ax0 XOR ay0;

dm(init_cmds) = ar;

ay0 = dm(init\_cmds+1);

ar = ax0 XOR ay0;

dm(init_cmds+1) = ar;

ay0 = dm(gain_state);

ar = ay0+1;

dm(gain_state) = ar;

ax0 = 0;

dm(chng_state) = ax0;

rts;

```

```

Sampling Rate Selection

*********

sampling wait:

if NOT FLAG_IN jump sampling_wait;

set sampling:

if NOT FLAG_IN jump done_config;

sr0 = dm(chng_state);

af = pass sr0;

if eq jump set_sampling;

ax0 = 0;

dm(chng_state) = ax0;

set rate:

ar = dm(sampling_state);

ar = pass ar;

if gt jump to_16;

/* buffer initialized for 8 kHz */

to_8:

ar = 1;

dm(sampling_state) = ar;

jump set_sampling;

to_16:

ax0 = dm(sampling_state);

ay0 = 1;

ar = ax0 - ay0;

if gt jump to_27;

ax1 = 0xc852;

/* set for 16.0 kHz */

dm(init\_cmds+8) = ax1;

ax0 = 2;

dm(sampling_state) = ax0;

jump set_sampling;

to_27:

ax0 = dm(sampling_state);

ay0 = 2;

ar = ax0 - ay0;

if gt jump to_32;

ax1 = 0xc854;

/* set for 27.42857 kHz */

dm(init\_cmds+8) = ax1;

ax0 = 3;

dm(sampling state) = ax0;

jump set_sampling;

```

(listing continues on next page)

```

to 32: ax0 = dm(sampling state);

ay0 = 3;

ar = ax0 - ay0;

if gt jump to_na;

ax1 = 0xc856;

/* set for 32.0 kHz */

dm(init cmds+8) = ax1;

ax0 = 4;

dm(sampling_state) = ax0;

jump set_sampling;

to_na:

ax0 = dm(sampling_state);

ay0 = 4;

ar = ax0 - ay0;

if gt jump to_na2;

ax0 = 5i

dm(sampling\_state) = ax0;

jump set_sampling;

to_na2: ax0 = dm(sampling_state);

ay0 = 5;

ar = ax0 - ay0;

if gt jump to_48;

ax0 = 6;

dm(sampling\_state) = ax0;

jump set_sampling;

to_48: ax0 = dm(sampling_state);

ay0 = 6;

ar = ax0 - ay0;

if gt jump to_96;

/* set for 48.0 kHz */

ax1 = 0xc85c;

dm(init\_cmds+8) = ax1;

ax0 = 7;

dm(sampling\_state) = ax0;

jump set_sampling;

to_96:

ax0 = dm(sampling_state);

ay0 = 7;

ar = ax0 - ay0;

if qt jump to 55;

/* set for 9.6 kHz */

ax1 = 0xc85e;

dm(init cmds+8) = ax1;

ax0 = 8;

dm(sampling state) = ax0;

jump set_sampling;

```

```

to 55: ax0 = dm(sampling state);

ay0 = 8;

ar = ax0 - ay0;

if gt jump to_11;

ax1 = 0xc851;

/* set for 5.5125 kHz */

dm(init cmds+8) = ax1;

ax0 = 9;

dm(sampling_state) = ax0;

jump set_sampling;

to_11: ax0 = dm(sampling_state);

ay0 = 9;

ar = ax0 - ay0;

if gt jump to_18;

ax1 = 0xc853;

/* set for 11.025 kHz */

dm(init\_cmds+8) = ax1;

ax0 = 10;

dm(sampling\_state) = ax0;

jump set_sampling;

to_18: ax0 = dm(sampling_state);

ay0 = 10;

ar = ax0 - ay0;

if gt jump to_22;

ax1 = 0xc855;

/* set for 18.9 kHz */

dm(init\_cmds+8) = ax1;

ax0 = 11;

dm(sampling\_state) = ax0;

jump set_sampling;

to_22:

ax0 = dm(sampling_state);

ay0 = 11;

ar = ax0 - ay0;

if gt jump to_37;

/* set for 22.05 kHz */

ax1 = 0xc857;

dm(init\_cmds+8) = ax1;

ax0 = 12;

dm(sampling\_state) = ax0;

jump set_sampling;

```

```

to 37: ax0 = dm(sampling state);

ay0 = 12;

ar = ax0 - ay0;

if gt jump to_44;

/* set for 37.8 kHz */

ax1 = 0xc859;

dm(init cmds+8) = ax1;

ax0 = 13;

dm(sampling_state) = ax0;

jump set_sampling;

to_44: ax0 = dm(sampling_state);

ay0 = 13;

ar = ax0 - ay0;

if gt jump to_33;

/* set for 44.1 kHz */

ax1 = 0xc85b;

dm(init\_cmds+8) = ax1;

ax0 = 14;

dm(sampling\_state) = ax0;

jump set_sampling;

to 33: ax0 = dm(sampling state);

ay0 = 14;

ar = ax0 - ay0;

if gt jump to_66;

/* set for 33.075 kHz */

ax1 = 0xc85d;

dm(init\_cmds+8) = ax1;

ax0 = 15;

dm(sampling\_state) = ax0;

jump set_sampling;

to_66: ax0 = 0;

dm(sampling\_state) = ax0;

ax1 = 0xc85f;

/* set for 6.615 kHz */

dm(init\_cmds+8) = ax1;

jump set_sampling;

done_config:

toggle FLAG_OUT;

jump sys init;

.endmod;

```

Listing 12.4 ADSP-2101/AD1847 Demonstration Routine (DEMO\_47.DSP)

### 12.3 INTERFACING DRAMS WITH THE ADSP-2100 FAMILY

As new algorithms for digital signal processors are developed, the memory requirements for these applications will continue to grow. Not only will these applications require more memory, but they will require increased efficiency for data storage and retrieval. Examples of these new applications include digital processing for two- and three-dimensional graphic images and speech storage for voice mail systems and digital telephone answering machines.

Two common storage options for these applications are Static Random Access Memories (SRAMs) and Dynamic Random Access Memories (DRAMs).

The functional difference between an SRAM and a DRAM is how the devices store data. In an SRAM, data is stored in transistors that hold their value until you overwrite them with new data. The DRAM stores data in capacitors that gradually loose their charge and, without refreshing, will loose the data.

Size is another important difference. Capacitors are significantly smaller than transistors, so DRAMs have a higher bit density.

Although a DRAM package is smaller than the equivalent memory size in an SRAM package, you should consider the following factors when you decide which memory device to use:

- Capacitor leakage.

Over time, DRAM capacitors "leak" or lose current and they must be "refreshed" periodically.

- Multiplexed-addressing.

To take advantage of the higher bit density of the DRAM, the capacitor cells are accessed using multiplexed-addressing. This reduces the required number of address pins because you can use each pin twice: once to address a memory row and a second time to address a memory column. Although this makes the package smaller, it complicates memory addressing.

- Availability, price, and performance.

DRAMs are readily available in 1 Mbit, 4 Mbit, and larger capacities, while SRAMs are typically available in 64 Kbyte (512 Kbit) and 128 Kbyte (1 Mbit) ranges. DRAMs are usually less expensive than SRAMs, but DRAM access times are significantly slower than SRAM access times.

Program and hardware simplicity.

The SRAM has a simple microprocessor interface. With N address lines, you can address 2<sup>N</sup> sequential locations in SRAM. You do not need additional software overhead (to refresh) when your program reads or writes to memory. Each read or write requires only a single DSP instruction. When using the ADSP-2100 family, each instruction takes one clock cycle. If necessary, wait states can be programmed for addressing slower memories.

When you use a DSP to address DRAM, you need additional hardware or software to handle the multiplexed row and column addressing and the refresh or precharge requirements. Many systems with DRAM use a hardware-intensive solution, like a DRAM controller.

As an alternative, you can move the control functions into the DSP software. This is a good implementation for systems requiring large memory spaces and cost efficient solutions. The chip count is reduced at the expense of decreased software throughput.

Although DSPs were designed to interface with SRAMs, in the right application, DRAMs can provide a larger, more cost-effective storage medium.

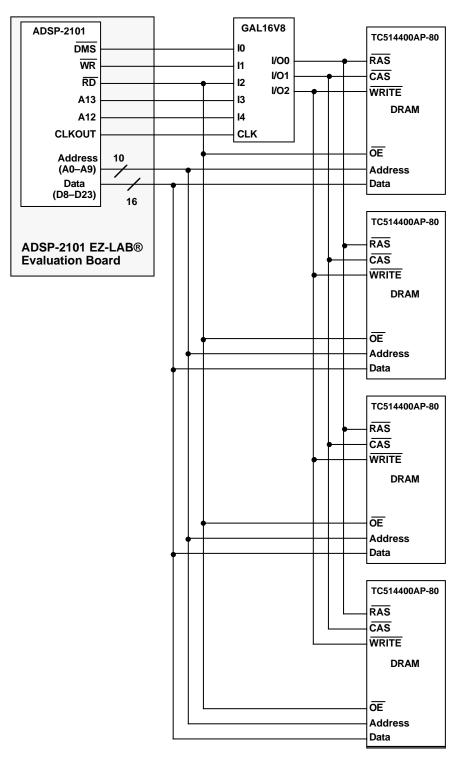

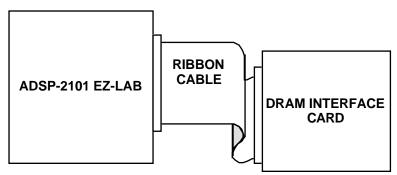

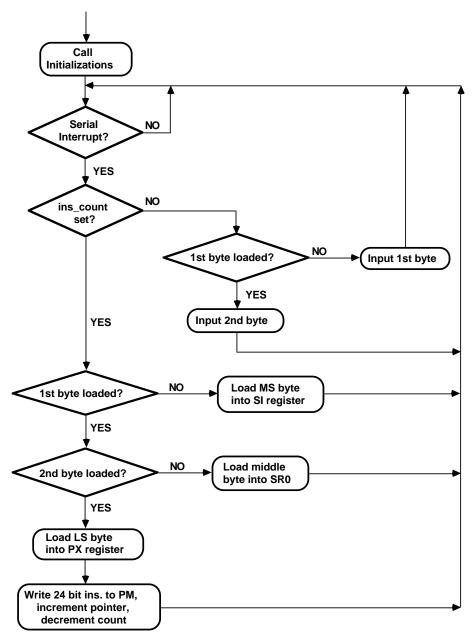

This chapter presents a software solution for addressing DRAM with the ADSP-2100 family. To implement this solution, the ADSP-2101 EZ-LAB® Evaluation Board was used as the development platform. A simple DRAM interface board was designed for this application. The DRAM interface board connects to the EZ-LAB through the expansion connector to let the EZ-LAB access the interface board's bank of memory. Figure 12.1 is a block diagram of the test system. The subroutines included at the end of this chapter were verified on this interface board and the ADSP-2101 EZ-LAB®.

Figure 12.1 Functional Block Diagram Of DRAM Interface Test System

Depending on your application and DRAM selection, you may have to modify the subroutines and the PAL equations included in this chapter.

Table 12.1 lists the components used in the test system described above.

| ADSP-2101 EZ-LAB Evaluation Board | 1 |

|-----------------------------------|---|

| 1 M x 4 DRAM, PN TC514400AP-80    | 4 |

| DRAM, 80 ns access time           |   |

| Programmable Logic Device,        |   |

| PN GAL16V8-15                     | 1 |

| Ribbon Cable Connector,           | 1 |

| 60-Pin, Straight wire-wrap        |   |

| Wire-wrap board                   | 1 |

### **Table 12.1 Test System Components**

When you design a DRAM memory system for an ADSP-2100 family DSP, you must consider the following points:

- DRAM configuration

- · Multiplexed memory addressing

- DSP and DRAM control signals

- DSP to DRAM Interface timing

- DRAM Memory access modes

- DRAM Refresh

### 12.3.1 DRAM Configuration

Originally, DRAMs were organized in one-bit widths, such as 256 K x 1 or 1 M x 1. Since ADSP-2100 family DSPs are 16-bit fixed point processors, it would have taken 16 DRAMs to store data memory. As DRAM chip organization evolves, larger memories and wider widths are becoming available. DRAMs are available up to 4 M and larger with 4-bit and 16-bit widths.

You must make a trade-off between system cost, power consumption, and available board space when you choose DRAMs. Larger and wider DRAMs are more expensive and consume more power than smaller DRAMs, but you need fewer chips for the same amount of memory.

For this application,  $1 \text{ M} \times 4 \text{ DRAMs}$  (available from several manufactures) were chosen. These four DRAMs provide  $1 \text{ M} \times 16$  data memory.

#### 12.3.2 Multiplexed Memory Addressing

To address a 1 M x 4 DRAM, you need ten address lines. With ten multiplexed address lines, you can address each row ( $2^{10}$ , or 1024 rows) and each column ( $2^{10}$ , or 1024 columns) in the DRAM. This is equal to 1024 x 1024, or 1 M, of addressable, 4-bit locations.

The ADSP-2100 family processors have 14 address lines for data memory. In an SRAM this can provide up to  $2^{14}$ , or 16,384 (16 K) addressable data memory locations. In this application, you only need ten address lines to address 4, 1 M x 4 DRAMs; this system uses A0–A9 of the ADSP-2101 (see Figure 12.1). Since the remaining address lines are not used to address memory, they could be left unconnected, but this system uses two available address lines (A12 and A13) as control lines for the DRAMs.

#### 12.3.3 DSP & DRAM Control Signals

To interface a DRAM to the DSP, compare the control signals and timing diagrams for both parts. Although this section has a brief overview of DSP and DRAM timing, you must determine the most effective use of the ADSP-2100 family control signals to control the reads and writes to DRAM in your application.

The DSP uses several control lines to access data memory: <u>RD</u>, <u>WR</u>, <u>DMS</u>. This application uses <u>DMS</u> (Data Memory Select) to differentiate between a program and data memory access because the program memory (PM) and data memory (DM) address and data lines are multiplexed off-chip.

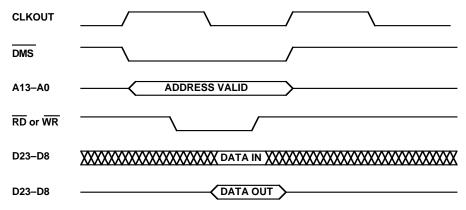

### 12.3.3.1 DSP Read/Write Timing

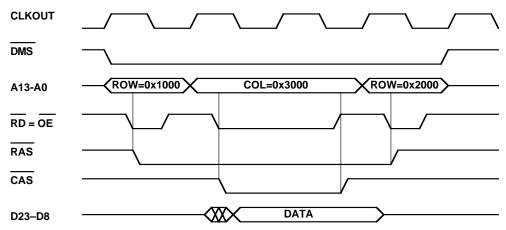

Figure 12.2 shows the read and write timing for the DSP. The read cycle (or write cycle) begins when the processor puts the address on the data memory address (DMA) bus and asserts <u>DMS</u>. The <u>RD</u> (or <u>WR</u>) signal is then asserted. Data is placed on the data bus within a specified time, then <u>RD</u> (or <u>WR</u>) is deasserted. Finally, <u>DMS</u> is deasserted, ending the memory access.

Figure 12.2 DSP Read/Write Timing

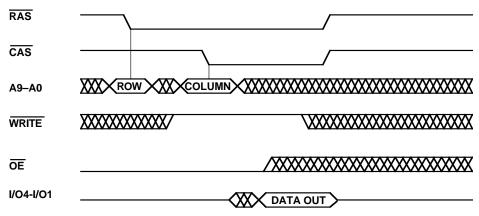

#### 12.3.3.2 DRAM Read/Write Timing

The DRAM uses the control signals <u>RAS</u> (Row Address Strobe), <u>CAS</u> (Column Address Strobe), <u>WRITE</u>, and <u>OE</u> (Output Enable).

A DRAM read cycle (see Figure 12.3 for the read cycle timing) starts when the falling edge of <u>RAS</u> strobes the row address into the DRAM. The falling edge of <u>CAS</u> strobes the column address into the DRAM and, after an access delay, enables the output buffer. The <u>WRITE</u> signal must stay high before and after the falling edge of <u>CAS</u>. The read cycle ends when the <u>RAS</u> and <u>CAS</u> lines are brought high.

Figure 12.3 DRAM Read Cycle Timing

Another read cannot occur until the precharge time is met after <u>RAS</u> and <u>CAS</u> are brought high. There are minimum pulse-widths and setup and hold times associated with all control lines.

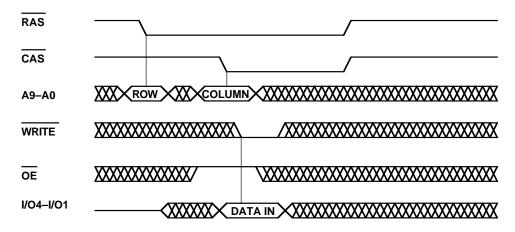

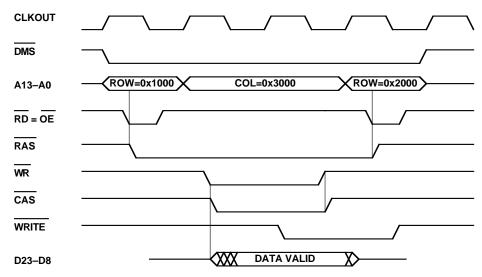

The DRAM write cycle is similar to the read cycle, except the <u>WRITE</u> line is held low. There are two basic write cycles for DRAMs: the early-write cycle and the delayed-write cycle. In the early-write cycle, the <u>WRITE</u> line is asserted before the assertion of <u>CAS</u>; in the delayed-write cycle, it is asserted after. For this DSP interface, use the delayed-write (or output enabled write) cycle.

A DRAM delayed-write cycle (write cycle timing shown in Figure 12.4) also starts when the falling edge of <u>RAS</u> strobes the row address into the DRAM. The falling edge of <u>CAS</u> strobes the column address into the DRAM. Then, the falling edge of <u>WRITE</u> latches the data into the DRAM. There are minimum pulse-widths and setup and hold times associated with these control lines as well.

Figure 12.4 DRAM Delayed-Write (Output Enabled) Cycle Timing

#### 12.3.3.3 RAS Generation

Because the falling edge of <u>RAS</u> latches the row address into the DRAM, the address must be valid before <u>RAS</u> is deasserted.

To drive <u>RAS</u>, use a combination of the <u>DMS</u>, <u>RD</u>, and address lines A13 and A12. A read from data memory locations 0x1000 to 0x13FF drives <u>RAS</u> low and latches the row address from 0x000 to 0x3FF. To drive <u>RAS</u> high again, read from any data memory address in the range 0x2000 to 0x27FF.

Use the following logic to drive **RAS**:

```

When (A13 = 0), (A12 = 1), (\underline{DMS} = 0), and (\underline{RD} = 0), \underline{RAS} = 0; or, when (A13 = 1), (A12 = 0), (\underline{DMS} = 0), and (\underline{RD} = 0), \underline{RAS} = 1; otherwise, RAS = RAS;

```

You can implement the above logic discretely, or in a PAL, such as the GAL16V8 used in this application.

12.3.3.4 CAS Generation

The generation of <u>CAS</u> must occur after the generation of <u>RAS</u>. Since the negative transition of <u>CAS</u> latches the column address into the DRAM, the address must be present before <u>CAS</u> goes low. To generate <u>CAS</u>, use the same control pins (<u>DMS, RD, WR, A13, and A12</u>). A read or write to the data memory addresses 0x3000 to 0x33FF drives <u>CAS</u> low and latches the column address from 0x000 to 0x3FF. (Note a read from data memory 0x3800 or higher reads from the DSP's internal data memory and does not assert the external <u>RD</u> or address lines.) <u>CAS</u> returns to logic high at the completion of the read or write (when <u>DMS</u> returns high).

Use the following logic to drive <u>CAS</u>:

```

When (A13 = 1), (A12 = 1), (DMS = 0), ((RD = 0)\#(WR = 0)), then CAS = 0; otherwise CAS = 1;

```

The actual read or write from the DSP occurs when <u>CAS</u> is low. To meet the write timing requirements of the DRAM and the DSP, <u>CAS</u> must be held low for two clock cycles. To accomplish this, use the external data memory wait states of the processor.

Data memory has several configurable wait states. The address range for <u>CAS</u> (0x3000–0x33FF) is configured by setting DWAIT3 in the data memory wait state control register. For this application, set DWAIT3 to 1.

#### 12.3.3.5 WRITE & OE Generation

The DRAM latches data on the falling edge of <u>WRITE</u>, while the DSP latches data on the rising edge. To ensure that the data from the DSP is still valid during the high-to-low transition of <u>WRITE</u>, the <u>WR</u> signal must be delayed one clock cycle. By delaying <u>WR</u> one cycle to create <u>WRITE</u>, you create a falling edge to latch valid data into the DRAM (see Figure 12.6). You can use a D flip-flop or PAL with registers to delay <u>WR</u>.

The  $\underline{RD}$  output of the DSP can be run directly into the  $\underline{OE}$  input of the DRAM.

#### 12.3.4 DSP To DRAM Interface Timing

This section describes the specific interface timing required between the DSP and DRAM.

#### 12.3.4.1 DRAM Read Timing

To read from the DRAM, the <u>OE</u> signal of the DRAM is tied to the DSP's <u>RD</u> line. Data is latched into the DSP on the rising edge of the <u>RD</u> signal and this matches the availability of data from the DRAM. Figure 12.5 shows the timing for generating the <u>RAS</u> and <u>CAS</u> signals to read from DRAM.

Figure 12.5 RAS & CAS Timing For DRAM Read

To accomplish the read cycle, execute a dummy read to a DM location (0x1000 to 0x13FF) to select a row and generate <u>RAS</u>. Follow this cycle with a read from external DM (0x3000 to 0x33FF), which selects a column, makes data available on bus lines, and latches it on the DSP. To finish the read cycle, perform a dummy read to a DM location (0x2000) to drive the <u>RAS</u> line high again.

Implemented in ADSP-2100 family assembly code, a DRAM read requires four DSP cycles. A fifth cycle (nop) is needed when consecutive reads are performed to assure <u>RAS</u> precharge timing is met. The following example illustrates a read from row address 0xABC and column address 0xDEF:

This may appear to be excessive overhead for a single memory read. You can achieve faster reads by using a DRAM with Fast-Page addressing (described later in this chapter).

#### 12.3.4.2 DRAM Write Timing

A write cycle is similar to a read cycle. For a write to the DRAM, the DSP's <u>WR</u> line must be delayed to create the DRAM <u>WRITE</u> signal. The DRAM <u>WRITE</u> signal is generated from a clocked D-flip flop within the GAL16V8 with the ADSP-2101 <u>WR</u> signal as input. The clock is obtained from DSP's CLKOUT signal. Figure 12.6 shows the timing for generating the <u>RAS</u> and <u>CAS</u> signals to write to DRAM.

Figure 12.6 RAS & CAS Timing For DRAM Write

For a delayed-write (or output-enable write), the falling edge of <u>WRITE</u> latches the data into the DRAM.

In ADSP-2100 family assembly code, a DRAM write requires four DSP cycles. A fifth cycle (nop) is needed when consecutive writes are performed to assure <u>RAS</u> precharge timing is met. The following example shows you how to write to row address 0xABC and column address 0xDEF:

#### 12.3.5 Memory Access Modes

DRAMs support several memory access modes to help reduce memory access times. The access mode that you select depends on the modes supported by the particular DRAM used in your application. Memory access modes include: Page Mode, Enhanced or Fast Page Mode, Static Column Mode, and Nibble or Ripple Mode. This section describes two modes: page mode and fast page mode.

#### 12.3.5.1 Page Mode

Page mode is the simplest memory access for a DRAM, but it also takes the longest time. To read one memory location requires a row and then a column access. A "page" is equivalent to a row.

Page-access provides quick access to memory locations in a page and can be accomplished by any DRAM. Page mode starts as a normal access when <u>RAS</u> is driven low. A memory access is accomplished by asserting <u>CAS</u> and performing a read or write. While keeping <u>RAS</u> low, you can access any other column location in the page by again asserting <u>CAS</u>. Since <u>RAS</u> remains low, the <u>RAS</u> precharge time is saved, which results in a faster access speed.

### 12.3.5.2 Enhanced Or Fast Page Mode

Fast page mode requires a DRAM that supports this feature. It is similar to page-mode access because you can access multiple columns within one page. However, it is faster than normal page mode because the column access is started as soon as the new address is placed on the DRAM address input. This saves the <u>CAS</u> precharge time.

Memory access in fast page mode is possible using the available signals. In this mode, memory reads or writes to dynamic memory are executed by leaving the  $\underline{RAS}$  signal low after the row latch occurs. You can continuously fill columns in the same row. The only limitation is that  $\underline{RAS}$  has a maximum pulse width timing requirement (for example 200  $\mu$ s).

Multiple reads or writes are performed much faster if done within the same page. The following example shows you how to read three locations in one row;

#### 12.3.6 DRAM Refresh

The DRAM stores data in capacitor cells. Since capacitors lose their charge, or "leak", over time, each cell of the DRAM must be refreshed periodically to maintain adequate voltage levels. Each memory read actually causes the capacitors to discharge slightly, so DRAMs have built-in write-back features that follow a read. This write-back feature is called a "precharge". The precharge occurs after the read when both <u>RAS</u> and <u>CAS</u> have returned high. It is part of the read cycle timing and you must account for it in timing analysis.

The read/write-back of the DRAM recharges the capacitor cells. The DRAM architecture refreshes every column cell when a row is accessed. Therefore, to accomplish a refresh of all memory cells, it is only necessary to read every DRAM row within the specified refresh period of your DRAM.

The <u>RAS</u>-only refresh is the simplest type of refresh operation and is supported by all DRAMs. To accomplish an <u>RAS</u>-only refresh, the <u>RAS</u> line is brought low one cycle for each row of the DRAM while the <u>CAS</u> remains high.

On the DRAM interface, this is done by reading from external data memory twice. One read sends  $\underline{RAS}$  low and latches the row address, the other read brings  $\underline{RAS}$  back high.  $\underline{CAS}$  ( $\underline{DMS}$ ) remains high through the entire  $\underline{RAS}$  cycle. The following example shows you one method to refresh DRAM.

**Note:** You may have to use a NOP instruction at the end of the refresh loop if the processor's instruction rate is less than 100 ns. The NOP instruction is necessary to meet the <u>RAS</u> precharge time and varies with DRAM access time (the DRAMs used in this application need a minimum <u>RAS</u> precharge time of 60 ns).

Some DRAMs have other refresh methods built-in. These include the hidden refresh, the CAS-before-RAS refresh, and refresh with scrubbing. For simplicity, this application concentrates on the RAS-only refresh.

#### 12.3.7 DRAM Refresh Timing

Typical DRAM refresh periods are 4–16 ms. Depending on your application, you can refresh all the rows at one time, called a burst refresh, or interleave refreshes with normal memory accesses, called an interleaved refresh.

If you use a 1 M deep DRAM with a 16 ms refresh period, you must access each of the 1024 rows during the 16 ms interval. The overall time needed to refresh the DRAM is the same regardless of whether you choose burst or interleaved refreshes. To refresh 1024 rows, you need 1024 x 2 cycles since it takes one cycle to assert  $\underline{RAS}$  and one cycle to deassert  $\underline{RAS}$ . For a DSP running at 10 MHz, there is a 100 ns cycle time. So, your 2048 cycles will take 2048 x 100 ns, or about 0.2 ms.

If your application can afford to pause for 0.2 ms every 16 ms, then the burst method is the simplest. If not, consider breaking the 0.2 ms into more manageable pieces, for example ten refreshes of 0.02 ms each.

Typical real-time applications are based on some periodic input or cycle. You can use this timing to determine when to perform the refresh. Otherwise, you must generate the period interrupt yourself to ensure that refresh occurs to prevent data loss. With ADSP-2100 family DSPs, you can use the internal timer to generate this periodic input. If the timer is not available, use an external interrupt through IRQ2. If the external interrupt is not available, use a serial port to create a periodic interrupt even if the port is not being used for communication.

The following code example refreshes all 1M DRAM locations within 16 ms. Since a 1M DRAM consists of 1024 rows x 1024 columns, you need to access 1024 rows within the 16 ms. The code uses the DSP's internal timer to create a periodic interrupt that refreshes 256 rows every 4 ms. For this example, assume the DSP is running at 16.67 MHz (60 ns clock cycle).

To refresh every 4 ms using 60 ns cycles, you need to create a timer interrupt every 4 ms/60 ns, or 66,667 clock cycles. If you set TSCALE to 2, TCOUNT is decremented every third clock cycle. Setting TCOUNT and TPERIOD to 22,222 or 0x56CE generates a timer interrupt every 66,666 cycles.

During a timer interrupt, the timer interrupt service routine calls the following refresh subroutine.

```

/* Refresh for 256 rows

bank1: 000-0FF

bank2: 100-1FF

bank3: 200-2FF

bank4: 300-3FF */

DRAM timer refresh:

/* determine which bank to refresh */

ax0=DM(bank);

ay0=0x3;

/* set ay0 for masking */

ay1=1; /* set ay1 for incrementing */

ar=ax0+ay0; /* update for next bank */

ar=ar and ay1; /* mask upper bits (bank = 0-3) */

DM(bank)=ar; /* store new bank for next refresh */

sr=lshift ar by 8 (lo); /* left shift bank by 8 */

M0=SR0;

I0=0x1000;

/* start of RAS addresses */

modify(I0,M0); /* offset to start of bank */

M1 = 1;

CNTR=256;

```

#### 12.3.8 EZ-LAB Implementation

To illustrate a DRAM interface to a DSP, this application uses the ADSP-2101 EZ-LAB evaluation board and a DRAM expansion card. The 2101 EZ-LAB has an ADSP-2101 processor and 64k x 8 EPROM. The EPROM is used only for booting the internal program RAM of the DSP. No additional data memory is on the board, however all data, address, and control lines are available through the connector.

To add DRAM to the EZ-LAB, the expansion card is connected to the EZ-LAB with a ribbon cable (see Figure 12.7). The DRAM interface card has one programmable logic device (GAL16V8), and four 1M x 4 DRAMs, (TC514400). Since the ADSP-2101 is a 16-bit fixed point DSP, the application needs four 1M x 4 DRAMs for 16-bit wide memory. The 16V8 PAL provides the glue logic to create the DRAM control signals, <u>RAS</u>, <u>CAS</u>, and <u>WRITE</u>.

Figure 12.7 EZ-LAB/DRAM Interface Board Connection

### 12.3.9 DRAM Program Listings

This section contains several program listings that were tested on the application described in this chapter.

```

.module/ram/boot=0 DRAM_read;

File Name: DRAMRD.DSP

Version: Version 0.00

Purpose: Conducts a random read from DRAM

Calling parameters:

setras: points to read location for RAS deassertion

i3: points to the row being accessed

i2: points to the column being accessed

Return Values

ax1: contains data stored in location (row = i3, column = i2)

Registers affected:

ax0, ax1, i2

Computation Time:

5 cycles

Random read from DRAM = 4 cycles ( dwait3 = 1)

* /

.external setras;

.entry read;

read: ax0 = dm(i3, m3);

/* select row for DRAM access */

/* read from column pointed by i2 */

ax1 = dm(i2, m2);

ax0 = dm(setras);

/* deassert RAS */

rts;

.endmod;

```

Listing 12.5 DRAM Read Program

```

.module/ram/boot=0 DRAM_write;

File Name: DRAMWR.DSP

Version: Version 0.00

Purpose: Conducts a random write to DRAM

Calling parameters:

setras: points to read location for RAS deassertion

i3: points to the row being accessed

i2: points to the column being accessed

mx0: contains the data that requires to be written

Return Values:

data in mx0 stored in location (row = i3, column = i2)

Registers affected:

ax0, i2

Computation Time:

5 cycles

Random (OE controlled write) to DRAM = 4 cycles ( dwait3 = 1)

* /

.external setras;

.entry write;

rts;

.endmod;

```

**Listing 12.6 DRAM Write Program**

```

.module/ram/boot=0 DRAM refresh;

File Name: DRAMREF.DSP

Version: Version 0.00

Purpose: Conduct memory accesses to DRAM for refresh

Calling Parameters:

refentr: has the number of rows to refresh

setras: points to the read location for RAS deassertion

i6: contains the address of the first row to refresh

Return Values:

Refresh of the number of rows specified by refentr

Registers Affected:

ax0, i6

Computation Time:

Total execution time = 3 + cntr(3) cycles;

RAS-only refresh per row = 3 cycles

.external refcntr;

.external setras;

.external row;

.entry refresh;

refresh: cntr = dm(refcntr);

/* number of rows to refresh */

do rasonly until ce;

ax0 = dm(i6, m6);

/* refresh row i6 */

/* deassert RAS */

ax0 = dm(setras);

/* inserted to meet RAS precharge */

rasonly: nop;

rts;

.endmod;

```

Listing 12.7 DRAM Refresh Program

```

.module/boot=0/abs=0 DRAM test;

File Name: DRAMTST.DSP

Version: Version 0.00

Purpose: Assembly source code for Dynamic memory test. This code was

written for the purpose of testing the DRAM interface board using

the EZ-ICE emulator. It accomodates testing of refresh as well as

independence of address lines.

It is designed with two sections, the first fills all of the

external DRAM and the second section reads and tests stored values

for errors.

This routine also sustains the DRAM storage using a timer

implemented burst refresh every 16ms.

Return Values:

buffer of 256 locations in internal data memory of error values

followed by the actual data values that should have been read back

from the DRAMs.

* /

.const rows = 1024;

.const cols = 1024;

/* number of rows */

/* number of columns */

.const ref_rows = 1024;

.const maxfill = 0xffff;

/* maximum fill value */

.var/dm/ram/seg=int_dm nbr_err, err_row, err_col, err_ov, buffer, refcntr;

.var/dm/ram/seg=row_deassert setras;

.var/dm/ram/seq=row range row;

.var/dm/ram/seg=col_range col;

.global row, setras, refcntr;

_____ Interrupt vectors _____ */

jump main; nop; nop; nop;

/* reset interrupt */

/* irq2 */

rti; nop; nop; nop;

rti; nop; nop; nop; rti; nop; nop; nop;

/* sport0 transmit */

/* sport0 receive */

/* sport1 transmit or irq1 */

rti; nop; nop; nop;

rti; nop; nop; nop;

/* sport1 receive or irq0 */

i6 = ^row; m6 = 0;

call refresh; rti;

/* timer expired */

____ External functions _____ */

.external refresh, write, read;

```

```

/* _____ Main ____ */

main: call setup;

ax0 = ref rows;

i3 = ^row;

m3 = 1;

13 = 0;

/* init. row pointer */

i2 = ^col;

m2 = 1;

12 = 0;

/* init. column pointer */

i4 = ^buffer;

m4 = 1;

/* Fill routine - This routine fills all of memory with values in the range of

0 to 0xffff using random writes (non-fast-page mode) so that address

line errors can be debugged. */

mx0 = 0;

/* for nested fill loop */

ay1 = 1;

/* increment value for fill counter*/

m3 = 0;

mr1 = 0;

do rowfill until ce;

i2 = ^col;

cntr = cols;

/* reset column pointer */

/* reset cntr to number of colums */

do colfill until ce;

imask = 0;

/* disable timer during write */

call write;

imask = 1;

ax1 = maxfill;

/* mx0 is the fill counter */

/* compare with max. fill value */

ay0 = mx0;

ayu + 1;

af = ax1 - ay0;

if eq ar

if eq ar = pass af; /* if mx0 = 0xffff, reset to 0 */

colfill: mx0 = ar;

```

```

/* Check routine - reads stored values and compares them to actual filled

values, if a difference is encountered in the read value it is

accumulated in the error routine, which stores actual and erroneous

values. */

reread: i3 = ^row;

/* reset row pointer */

/* reset column pointer */

i2 = ^col;

mr0 = 0;

/* mr0 = check counter */

cntr = rows;

/* cntr = number of rows */

do rowread until ce;

i2 = ^col;

cntr = cols;

do colread until ce;

imask = 0;

/* disable timer during read */

call read;

imask = 1;

ay0 = mr0;

ar = dm(nbr_err);

af = ax1 - av0;

if ne call error;

ax1 = maxfill;

ar = ay0 + 1;

af = ax1 - ay0;

if eq ar = pass af; /* if mr0 = 0xffff, reset it to 0 */

colread: mr0 = ar;

/* increment row pointer */

rowread: modify(i3,m2);

sr1 = dm(nbr err);

/* sr1 + mr0 = number of errors */

mr0 = dm(err ov);

ar = sr1;

/* this tests refresh ability */

/* continually **

ar = pass ar;

if eq jump reread;

/* continually read until error */

wait: idle;

/* set breakpoint here in emulation */

jump wait;

/* _____ End Main ____ */

error: ay1 = maxfill;

ar = dm(nbr_err);

af = ar - ay1;

/* add it to nbr_err or err_ov */

if ne jump not_ov;

ay1 = 1;

ax1 = dm(err ov);

ar = ax1 + ay1;

dm(err_ov) = ar;

jump cont;

```

```

not ov: ay1 = 1;

ar = ar + ay1;

/* save 256 error values */

dm(nbr_err) = ar;

cont: dm(i4, m4) = ax1;

/* saves error value followed by */

/* actual value in internal DM */

dm(i4, m4) = ay0;

dm(err row) = i3;

/* saves last error row and */

dm(err_col) = i2;

/* column location */

setup: ax0 = 0x0003;

dm(0x3ffb) = ax0;

/* TSCALE */

ax0 = 0xc350;

/* 50,000 for 16ms per interrupt */

dm(0x3ffc) = ax0;

/* TCOUNT */

dm(0x3ffd) = ax0;

/* TPERIOD */

ax0=0x0200;

dm(0x3ffe)=ax0;

/* dWait3 = 1 WS */

ax0=0x00000;

dm(0x3ffa)=ax0;

/* No Sport functions enabled */

dm(0x3ff9)=ax0;

dm(0x3ff8)=ax0;

dm(0x3ff7)=ax0;

dm(0x3ff6)=ax0;

dm(0x3ff5)=ax0;

dm(0x3ff4)=ax0;

dm(0x3ff3)=ax0;

dm(0x3ff2)=ax0;

dm(0x3ff1)=ax0;

dm(0x3ff0)=ax0;

dm(0x3fef)=ax0;

dm(0x3fff)=ax0;

rts;

.endmod;

```

**Listing 12.8 DRAM Test Program**

```

.module/boot=0/abs=0 DRAM record;

File Name: DRAMRCRD.DSP

Version: Version 0.00

Purpose: Assembly source code for u-law companded speech sample

storage and playback. This routine enables approximately

2 minutes and 11 seconds of storage on the DRAM interface

board. The maximum storage time possible is twice that

mentioned above using u-law companding (8-bit word length).

Return Values:

IRQ2 - switch between record and forward playback

FLAG_IN - switch between foward and backward playback.

Note: pressing FLAG_IN in record mode causes backward

playback.

record mode - flag_out is low

playback mode - flag_out is high

* /

.const rows = 0x400; /* # of rows and columns on 1M DRAM */

.const cols = 0x400;

.const lastrow = 0x13ff;

.const lastcol = 0x33ff;

.const ref_rows = 0x10;

.global row, setras, refcntr;

rti; nop; nop; nop; nop; /* sport0 transmit */

jump record; nop; nop; /* sport0 receive */

rti; nop; nop; nop; /* sport1 transmit or irq1 */

rti; nop; nop; nop; /* sport1 receive or irq0 */

rti; nop; nop; nop; /* timer expired */