## ADD / ADD with CARRY **15**

$[IF cond] | AR | = xo_{Y}$ + yop + C + yop + C + constant Syntax: = xop constant + CPermissible conds (see Table 15.9) *Permissible xops Permissible yops* AX0 MR2 AY0 EO LE AC AX1 AY1 NE NEG NOT AC MR1 AR MR0 AF GT POS MV SR1 GE AV NOT MV NOT AV NOT CE SR0 LT

*Permissible constants* (*ADSP-217x*, *ADSP-218x*, *ADSP-21msp58/59 only*) 0, 1, 2, 4, 8, 16, 32, 64, 128, 256, 512, 1024, 2048, 4096, 8192, 16384, 32767 -2, -3, -5, -9, -17, -33, -65, -129, -257, -513, -1025, -2049, -4097, -8193, -16385, -32768

| Example: | IF EQ AR = $AX0 + AY0 + C$ ; |

|----------|------------------------------|

| -        | AR = AR + 512;               |

**Description:** Test the optional condition and, if true, perform the specified addition. If false then perform a no-operation. Omitting the condition performs the addition unconditionally. The addition operation adds the first source operand to the second source operand along with the ALU carry bit, AC, (if designated by the "+C" notation), using binary addition. The result is stored in the destination register. The operands are contained in the data registers or constant specified in the instruction.

The *xop* + *constant* operation is only available on the ADSP-217x, ADSP-218x, and ADSP-21msp58/59 processors and may not be used in multifunction instructions.

#### **Status Generated:**

| ASTAT: | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|--------|----|----|----|----|----|----|----|----|

|        | SS | MV | AQ | AS | AC | AV | AN | AZ |

|        | _  | _  | _  | _  | *  | *  | *  | *  |

- AZ Set if the result equals zero. Cleared otherwise.

- AN Set if the result is negative. Cleared otherwise.

- AV Set if an arithmetic overflow occurs. Cleared otherwise.

- AC Set if a carry is generated. Cleared otherwise.

#### (instruction continues on next page)

## **15** ALU ADD / ADD with CARRY

#### **Instruction Format:**

Conditional ALU/MAC operation, Instruction Type 9:

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16  | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2  | 1   | 0 |

|----|----|----|----|----|----|----|-----|----|----|----|----|----|----|---|---|---|---|---|---|---|----|-----|---|

| 0  | 0  | 1  | 0  | 0  | Z  |    | AME | 7  |    |    | Υc | pp | Xc | p |   | 0 | 0 | 0 | 0 |   | CC | ONE | ) |

AMF specifies the ALU or MAC operation, in this case:

AMF = 10010 for xop + yop + CAMF = 10011 for xop + yop

(Note that xop + C is a special case of xop + yop + C with yop=0.)

| Z:   | Destination register | Yop:  | Y operand |

|------|----------------------|-------|-----------|

| Хор: | X operand            | COND: | condition |

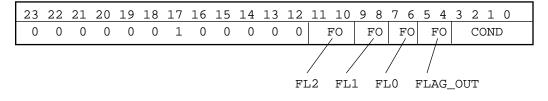

(*xop* + *constant*) Conditional ALU/MAC operation, Instruction Type 9: (*ADSP-217x*, *ADSP-218x*, *ADSP-21msp58/59 only*)

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16  | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | б | 5 | 4  | 3 | 2  | 1   | 0 |

|----|----|----|----|----|----|----|-----|----|----|----|----|----|----|---|---|---|---|---|----|---|----|-----|---|

| 0  | 0  | 1  | 0  | 0  | Z  |    | AME | 7  |    |    | 7  | ΥY | Xc | p |   | C | C | E | 30 |   | CC | ONE | ) |

AMF specifies the ALU or MAC operation, in this case:

AMF = 10010 for xop + constant + C AMF = 10011 for xop + constant

Z: Destination register COND: condition Xop: X operand

BO, CC, and YY specify the constant (see Appendix A, Instruction Coding).

### SUBTRACT X-Y / SUBTRACT X-Y with BORROW 15

Syntax: AR AF [IF cond] хор yop yop + C-1+ C-1 - constant - constant + C-1Permissible conds (see Table 15.9) *Permissible xops Permissible yops* AX0 MR2 AY0 EQ LE AC MR1 NE NEG NOT AC AX1 AY1 AR MR0 AF GT POS MV SR1 GE AV NOT MV SR0 LT NOT AV NOT CE

*Permissible constants* (*ADSP-217x*, *ADSP-218x*, *ADSP-21msp58/59 only*) 0, 1, 2, 4, 8, 16, 32, 64, 128, 256, 512, 1024, 2048, 4096, 8192, 16384, 32767 -2, -3, -5, -9, -17, -33, -65, -129, -257, -513, -1025, -2049, -4097, -8193, -16385, -32768

**Example:** IF GE AR = AX0 - AY0;

**Description:** Test the optional condition and, if true, then perform the specified subtraction. If the condition is not true then perform a no-operation. Omitting the condition performs the subtraction unconditionally. The subtraction operation subtracts the second source operand from the first source operand, and optionally adds the ALU Carry bit (AC) minus 1 (H#0001), and stores the result in the destination register. The (C–1) quantity effectively implements a borrow capability for multiprecision subtractions. The operands are contained in the data registers or constant specified in the instruction.

The *xop* – *constant* operation is only available on the ADSP-217x, ADSP-218x, and ADSP-21msp58/59 processors and may not be used in multifunction instructions.

#### **Status Generated:**

| ASTAT: | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|--------|----|----|----|----|----|----|----|----|

|        | SS | MV | AQ | AS | AC | AV | AN | AZ |

|        | -  | -  | -  | -  | *  | *  | *  | *  |

- AZ Set if the result equals zero. Cleared otherwise.

- AN Set if the result is negative. Cleared otherwise.

AV Set if an arithmetic overflow occurs. Cleared otherwise.

(instruction continues on next page)

### 15 ALU SUBTRACT X-Y / SUBTRACT X-Y with BORROW

AC Set if a carry is generated. Cleared otherwise.

### **Instruction Format:**

Conditional ALU/MAC operation, Instruction type 9:

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15  | 14 | 13 | 12 | 11 | 10 | 9  | 8 | 7 | 6 | 5 | 4 | 3 | 2  | 1   | 0 |

|----|----|----|----|----|----|----|----|-----|----|----|----|----|----|----|---|---|---|---|---|---|----|-----|---|

| 0  | 0  | 1  | 0  | 0  | Z  |    |    | AME | ק  |    | Yc | p  | Xc | pp |   | 0 | 0 | 0 | 0 |   | CC | ONE | ) |

AMF specifies the ALU or MAC operation. In this case,

AMF = 10110 for xop - yop + C - 1 operation. AMF = 10111 for xop - yop operation.

Note that xop + C - 1 is a special case of xop - yop + C - 1 with yop=0.

| Z:   | Destination register | Yop:  | Y operand |

|------|----------------------|-------|-----------|

| Хор: | X operand            | COND: | condition |

(*xop – constant*) Conditional ALU/MAC operation, Instruction Type 9: (*ADSP-217x*, *ADSP-218x*, *ADSP-21msp58/59 only*)

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16  | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8 | 7 | б | 5 | 4  | 3 | 2  | 1   | 0 |  |

|----|----|----|----|----|----|----|-----|----|----|----|----|----|----|----|---|---|---|---|----|---|----|-----|---|--|

| 0  | 0  | 1  | 0  | 0  | Z  |    | AME | 7  |    |    | Z  | ζΥ | Xc | pp |   | C | C | E | 30 |   | CC | ONE | ) |  |

AMF specifies the ALU or MAC operation, in this case:

AMF = 10110 for xop - constant + C - 1 AMF = 10111 for xop - constant

Z: Destination register COND: condition Xop: X operand

BO, CC, and YY specify the constant (see Appendix A, Instruction Coding).

### SUBTRACT Y-X / SUBTRACT Y-X with BORROW 15

| Syntax: [IF                                                    | cond ] $\begin{vmatrix} AR \\ AF \end{vmatrix}$ = | -xop + 0<br>-xop + c                  |                                                    |                                                          |

|----------------------------------------------------------------|---------------------------------------------------|---------------------------------------|----------------------------------------------------|----------------------------------------------------------|

| Permissible xops<br>AX0 MR2<br>AX1 MR1<br>AR MR0<br>SR1<br>SR0 | Permissible yops<br>AY0<br>AY1<br>AF              | Permiss<br>EQ<br>NE<br>GT<br>GE<br>LT | sible conds (s<br>LE<br>NEG<br>POS<br>AV<br>NOT AV | ee Table 15.9)<br>AC<br>NOT AC<br>MV<br>NOT MV<br>NOT CE |

*Permissible constants* (*ADSP-217x*, *ADSP-218x*, *ADSP-21msp58/59 only*) 0, 1, 2, 4, 8, 16, 32, 64, 128, 256, 512, 1024, 2048, 4096, 8192, 16384, 32767 -2, -3, -5, -9, -17, -33, -65, -129, -257, -513, -1025, -2049, -4097, -8193, -16385, -32768

**Example:** IF GT AR = AY0 - AX0 + C - 1;

**Description:** Test the optional condition and, if true, then perform the specified subtraction. If the condition is not true then perform a no-operation. Omitting the condition performs the subtraction unconditionally. The subtraction operation subtracts the second source operand from the first source operand, optionally adds the ALU Carry bit (AC) minus 1 (H#0001), and stores the result in the destination register. The (C–1) quantity effectively implements a borrow capability for multiprecision subtractions. The operands are contained in the data registers or constant specified in the instruction.

The -xop + constant operation is only available on the ADSP-217x, ADSP-218x, and ADSP-21msp58/59 processors and may not be used in multifunction instructions.

### **Status Generated:**

| ASTAT: |   | 7 | 6 | 5 | 4 | 3 | 2 | 1  | 0 |

|--------|---|---|---|---|---|---|---|----|---|

|        |   |   |   |   |   |   |   | AN |   |

|        |   | — | — | _ | _ | * | * | *  | * |

|        | _ |   |   | _ | _ | _ |   |    |   |

AZ Set if the result equals zero. Cleared otherwise.

AN Set if the result is negative. Cleared otherwise.

(instruction continues on next page)

### 15 ALU SUBTRACT Y-X / SUBTRACT Y-X with BORROW

AV Set if an arithmetic overflow occurs. Cleared otherwise.

AC Set if a carry is generated. Cleared otherwise.

### **Instruction Format:**

Conditional ALU/MAC Operation, Instruction Type 9:

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15  | 14 | 13 | 12 | 11 | 10 | 9   | 8 | 7 | 6 | 5 | 4 | 3 | 2  | 1   | 0 |

|----|----|----|----|----|----|----|----|-----|----|----|----|----|----|-----|---|---|---|---|---|---|----|-----|---|

| 0  | 0  | 1  | 0  | 0  | Z  |    | I  | \MF |    |    | Υc | pp | Σ  | ζop | ~ | 0 | 0 | 0 | 0 |   | CC | ONE | ) |

AMF specifies the ALU or MAC operation. In this case,

AMF = 11010 for yop - xop + C - 1AMF = 11001 for yop - xop

(Note that -xop + C - 1 is a special case of yop - xop + C - 1 with yop=0.)

| Z:   | Destination register | Yop:  | Y operand |

|------|----------------------|-------|-----------|

| Хор: | X operand            | CÔND: | condition |

(*-xop* + *constant*) Conditional ALU/MAC operation, Instruction Type 9: (*ADSP-217x*, *ADSP-218x*, *ADSP-21msp58/59* only)

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16  | 15       | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | б | 5 | 4  | 3 | 2  | 1   | 0 |

|----|----|----|----|----|----|----|-----|----------|----|----|----|----|----|---|---|---|---|---|----|---|----|-----|---|

| 0  | 0  | 1  | 0  | 0  | Z  |    | AME | <u>r</u> |    |    | 7  | ζΥ | Хc | p |   | C | C | E | 30 |   | CC | ONE | ) |

AMF specifies the ALU or MAC operation, in this case:

AMF = 11010 for constant - xop + C - 1 AMF = 11001 for constant - xop

Z: Destination register COND: condition Xop: X operand

BO, CC, and YY specify the constant (see Appendix A, Instruction Coding).

## AND, OR, XOR 15

;

| Synta                      | <b>X:</b> [IF o                                | cond ]                          | $\left  AR \\ AF \right  =$ | хор                                   | AND<br>OR<br>XOR                                   | yop<br>constant                                          |

|----------------------------|------------------------------------------------|---------------------------------|-----------------------------|---------------------------------------|----------------------------------------------------|----------------------------------------------------------|

| Permis<br>AX0<br>AX1<br>AR | ssible xops<br>MR2<br>MR1<br>MR0<br>SR1<br>SR0 | Permissible<br>AY0<br>AY1<br>AF | e yops                      | Permiss<br>EQ<br>NE<br>GT<br>GE<br>LT | sible conds (s<br>LE<br>NEG<br>POS<br>AV<br>NOT AV | ee Table 15.9)<br>AC<br>NOT AC<br>MV<br>NOT MV<br>NOT CE |

*Permissible constants* (*ADSP-217x*, *ADSP-218x*, *ADSP-21msp58/59 only*) 0, 1, 2, 4, 8, 16, 32, 64, 128, 256, 512, 1024, 2048, 4096, 8192, 16384, 32767 -2, -3, -5, -9, -17, -33, -65, -129, -257, -513, -1025, -2049, -4097, -8193, -16385, -32768

| Example: | AR = AX0 XOR AY0;             |

|----------|-------------------------------|

|          | IF FLAG_IN AR = MR0 AND 8192; |

**Description:** Test the optional condition and if true, then perform the specified bitwise logical operation (logical AND, inclusive OR, or exclusive OR). If the condition is not true then perform a no-operation. Omitting the condition performs the logical operation unconditionally. The operands are contained in the data registers or constant specified in the instruction.

The *xop AND/OR/XOR constant* operation is only available on the ADSP-217x, ADSP-218x, and ADSP-21msp58/59 processors and may not be used in multifunction instructions.

#### Status Generated:

| ASTAT: | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|--------|----|----|----|----|----|----|----|----|

|        | SS | MV | AQ | AS | AC | AV | AN | AZ |

|        | _  | -  | _  | -  | 0  | 0  | *  | *  |

- AZ Set if the result equals zero. Cleared otherwise.

- AN Set if the result is negative. Cleared otherwise.

- AV Always cleared.

- AC Always cleared.

(instruction continues on next page)

## **15** ALU AND, OR, XOR

### **Instruction Format:**

Conditional ALU/MAC Operation, Instruction Type 9:

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15  | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2  | 1   | 0 |

|----|----|----|----|----|----|----|----|-----|----|----|----|----|----|---|---|---|---|---|---|---|----|-----|---|

| 0  | 0  | 1  | 0  | 0  | Z  |    |    | AME | 7  |    | Υc | p  | Xc | p |   | 0 | 0 | 0 | 0 |   | CC | DNE | ) |

AMF specifies the ALU or MAC operation. In this case,

AMF = 11100 for AND operation. AMF = 11101 for OR operation. AMF = 11110 for XOR operation.

| Z:   | Destination register | Yop:  | Y operand |

|------|----------------------|-------|-----------|

| Xop: | X operand            | COND: | condition |

#### (xop AND/OR/XOR constant)

Conditional ALU/MAC operation, Instruction Type 9: (ADSP-217x, ADSP-218x, ADSP-21msp58/59 only)

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16  | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | б | 5 | 4  | 3 | 2  | 1   | 0 |  |

|----|----|----|----|----|----|----|-----|----|----|----|----|----|----|---|---|---|---|---|----|---|----|-----|---|--|

| 0  | 0  | 1  | 0  | 0  | Z  |    | AME | ק  |    |    | Z  | ζΥ | Хо | p |   | С | C | E | 30 |   | CC | ONE | ) |  |

AMF specifies the ALU or MAC operation, in this case:

AMF = 11100 for AND operation. AMF = 11101 for OR operation. AMF = 11110 for XOR operation.

Z:Destination registerCOND: conditionXop:X operand

BO, CC, and YY specify the constant (see Appendix A, Instruction Coding).

### ALU TEST BIT, SET BIT, CLEAR BIT, TOGGLE BIT (ADSP-217x, ADSP-218x, ADSP-21msp58/59 only)

;

15

Syntax:[ IF cond ]AR<br/>AF=TSTBIT n OF xop<br/>SETBIT n OF xop<br/>CLRBIT n OF xop<br/>TGLBIT n OF xop

| Permi | ssible xops | Pern | issible conds | s (see Table 15.9) |

|-------|-------------|------|---------------|--------------------|

|       | MR2         | EQ   | LE            | AC                 |

| AX1   | MR1         | NE   | NEG           | NOT AC             |

| AR    | MR0         | GT   | POS           | MV                 |

|       | SR1         | GE   | AV            | NOT MV             |

|       | SR0         | LT   | NOT AV        | NOT CE             |

*Permissible n values (0=LSB)* 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15

| Examples: | AF=TSTBIT 5 OF AR;   |

|-----------|----------------------|

|           | AR=TGLBIT 13 OF AX0; |

**Description:** Test the optional condition and if true, then perform the specified bit operation. If the condition is not true then perform a no-operation. Omitting the condition performs the operation unconditionally. These operations cannot be used in multifunction instructions.

These operations are defined as follows:

TSTBIT is an AND operation with a 1 in the selected bit SETBIT is an OR operation with a 1 in the selected bit CLRBIT is an AND operation with a 0 in the selected bit TGLBIT is an XOR operation with a 1 in the selected bit

The ASTAT status bits are affected by these instructions. The following instructions could be used, for example, to test a bit and branch accordingly:

AF=TSTBIT 5 OF AR; IF NE JUMP set; /\*Jump to "set" if bit 5 of AR is set\*/

#### **Status Generated:**

| ASTAT: | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|--------|----|----|----|----|----|----|----|----|

|        | SS | MV | AQ | AS | AC | AV | AN | AZ |

|        | _  | _  | _  | _  | 0  | 0  | *  | *  |

### 15 ALU TEST BIT, SET BIT, CLEAR BIT, TOGGLE BIT (ADSP-217x, ADSP-218x, ADSP-21msp58/59 only)

- AZ Set if the result equals zero. Cleared otherwise.

- AN Set if the result is negative. Cleared otherwise.

- AV Always cleared.

- AC Always cleared.

#### **Instruction Format:**

(xop AND/OR/XOR constant) Conditional ALU/MAC operation, Instruction Type 9: (ADSP-217x, ADSP-218x, ADSP-21msp58/59 only)

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16  | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | б | 5 | 4  | 3 | 2  | 1   | 0 |

|----|----|----|----|----|----|----|-----|----|----|----|----|----|----|---|---|---|---|---|----|---|----|-----|---|

| 0  | 0  | 1  | 0  | 0  | Z  |    | AME | ק  |    |    | Z  | ζΥ | Хc | p |   | C | C | E | 30 |   | CC | ONE | ) |

AMF specifies the ALU or MAC operation, in this case:

AMF = 11100 for AND operation. AMF = 11101 for OR operation. AMF = 11110 for XOR operation.

| Z:   | Destination register | COND: | condition |

|------|----------------------|-------|-----------|

| Хор: | X operand            |       |           |

## PASS/CLEAR 15

BO, CC, and YY specify the constant (see Appendix A, Instruction Coding).

| Synta  | <b>X:</b> [IF o | cond ]     | AR<br>AF | = | PASS     | xop<br>yop<br>constant | ;              |

|--------|-----------------|------------|----------|---|----------|------------------------|----------------|

| Permis | ssible xops     | Permissibl | e yops   |   | Permissi | ble conds (s           | ee Table 15.9) |

| AX0    | MR2             | AY0        | 0,       |   | EQ       | LE                     | AC             |

| AX1    | MR1             | AY1        |          |   | NE       | NEG                    | NOT AC         |

| AR     | MR0             | AF         |          |   | GT       | POS                    | MV             |

|        | SR1             |            |          |   | GE       | AV                     | NOT MV         |

|        | SR0             |            |          |   | LT       | NOT AV                 | NOT CE         |

*Permissible constants* (all ADSP-21xx processors) -1, 0, 1

Permissible constants (ADSP-217x, ADSP-218x, ADSP-21msp58/59 only) 2, 3, 4, 5, 7, 8, 9, 15, 16, 17, 31, 32, 33, 63, 64, 65, 127, 128, 129, 255, 256, 257, 511, 512, 513, 1023, 1024, 1025, 2047, 2048, 2049, 4095, 4096, 4097, 8191, 8192, 8193, 16383, 16384, 16385, 32766, 32767 -2, -3, -4, -5, -6, -8, -9, -10, -16, -17, -18, -32, -33, -34, -64, -65, -66, -128, -129, -130, -256, -257, -258, -512, -513, -514, -1024, -1025, -1026, -2048, -2049, -2050, -4096, -4097, -4098, -8192, -8193, -8194, -16384, -16385, -16386, -32767, -32768 **Examples:** IF GE AR = PASS AY0;

AR = PASS 0; $AR = PASS 8191; \qquad (ADSP-217x, ADSP-218x, ADSP-21msp58/59 only)$

**Description:** Test the optional condition and if true, pass the source operand unmodified through the ALU block and store in the destination register. If the condition is not true perform a no-operation. Omitting the condition performs the PASS unconditionally. The source operand is contained in the data register or constant specified in the instruction.

PASS 0 is one method of clearing AR. PASS 0 can also be combined with memory reads and writes in a multifunction instruction to clear AR.

The PASS instruction performs the transfer to the AR or AF register and affects the ASTAT status flags (for xop, yop, -1, 0, 1 only). This instruction is different from a register move operation which does not affect any status flags. The *PASS constant*

### 15 ALU PASS/CLEAR

operation (using any constant other than -1, 0, or 1) causes the ASTAT status flags to be undefined.

The *PASS constant* operation (using any constant other than –1, 0, or 1) is only available on the ADSP-217x, ADSP-218x, and ADSP-21msp58/59 processors and may not be used in multifunction instructions.

### **Status Generated:**

| ASTAT: | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|--------|----|----|----|----|----|----|----|----|

|        | SS | MV | AQ | AS | AC | AV | AN | AZ |

|        | _  | _  | _  | _  | 0  | 0  | *  | *  |

AZ Set if the result equals zero. Cleared otherwise.

AN Set if the result is negative. Cleared otherwise.

AV, AC Always cleared.

Note: The *PASS constant* operation (using any constant other than –1, 0, or 1) causes the ASTAT status flags to be undefined.

#### **Instruction Format:**

Conditional ALU/MAC Operation, Instruction Type 9:

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15  | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2  | 1  | 0 |

|----|----|----|----|----|----|----|----|-----|----|----|----|----|----|---|---|---|---|---|---|---|----|----|---|

| 0  | 0  | 1  | 0  | 0  | Z  |    |    | AMI | 7  |    | Yo | qc | Xc | p |   | 0 | 0 | 0 | 0 |   | CO | ND | ) |

AMF specifies the ALU or MAC operation. In this case,

AMF = 10000 for PASS yop AMF = 10011 for PASS xop AMF = 10001 for PASS 1 AMF = 11000 for PASS -1

Note that PASS xop is a special case of xop + yop, with yop=0. Note that PASS 1 is a special case of yop + 1, with yop=0. Note that PASS -1 is a special case of yop -1, with yop=0.

| Z:   | Destination register | Yop:  | Y operand |

|------|----------------------|-------|-----------|

| Хор: | X operand            | CÔND: | condition |

Conditional ALU/MAC operation, Instruction Type 9: (*PASS constant; constant*  $\neq$  0,1,-1) (*ADSP*-217x, *ADSP*-218x, *ADSP*-21msp58/59 only)

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16  | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8 | 7 | 6  | 5 | 4  | 3 | 2  | 1   | 0 |

|----|----|----|----|----|----|----|-----|----|----|----|----|----|----|----|---|---|----|---|----|---|----|-----|---|

| 0  | 0  | 1  | 0  | 0  | Z  |    | AMF | 7  |    |    | 2  | ζΥ | Xc | pp |   | C | CC | E | 30 |   | CC | ONE | ) |

AMF specifies the ALU or MAC operation. In this case,

| AMF = 10000 for PASS yop      | (special case of yop, with yop=constant)     |

|-------------------------------|----------------------------------------------|

| AMF = 10001  for PASS yop + 1 | (special case of yop + 1, with yop=constant) |

| AMF = 11000  for PASS yop - 1 | (special case of yop – 1, with yop=constant) |

### ALU 15

| Z:   | Destination register | COND: | condition |

|------|----------------------|-------|-----------|

| Хор: | X operand            |       |           |

BO, CC, and YY specify the constant (see Appendix A, Instruction Coding).

| Synta                     | <b>X:</b> [IF                                  | cond ] AI<br>AI                    | $\left  \frac{R}{2} \right  = -$ | xop<br>yop                  | ;                                                |                                                          |

|---------------------------|------------------------------------------------|------------------------------------|----------------------------------|-----------------------------|--------------------------------------------------|----------------------------------------------------------|

| Permi<br>AX0<br>AX1<br>AR | ssible xops<br>MR2<br>MR1<br>MR0<br>SR1<br>SR0 | Permissible yc<br>AY0<br>AY1<br>AF | E<br>N<br>C                      | Q L<br>JE N<br>GT P<br>GE A | le conds (se<br>LE<br>NEG<br>POS<br>AV<br>NOT AV | ee Table 15.9)<br>AC<br>NOT AC<br>MV<br>NOT MV<br>NOT CE |

**Example:** IF LT AR = -AY0;

**Description:** Test the optional condition and if true, then NEGATE the source operand and store in the destination location. If the condition is not true then perform a no-operation. Omitting the condition performs the NEGATE operation unconditionally. The source operand is contained in the data register specified in the instruction.

#### **Status Generated:**

| ASTAT: | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|--------|----|----|----|----|----|----|----|----|

|        | SS | MV | AQ | AS | AC | AV | AN | ΑZ |

|        | _  | _  | _  | _  | *  | *  | *  | *  |

| AZ | Set if the result equals zero. Cleared otherwise. |

|----|---------------------------------------------------|

| AN | Set if the result is negative. Cleared otherwise. |

| AV | Set if operand = H#8000. Cleared otherwise.       |

|    |                                                   |

AC Set if operand equals zero. Cleared otherwise.

### **Instruction Format:**

Conditional ALU/MAC Operation, Instruction Type 9:

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15  | 14 | 13 | 12 | 11 | 10 | 9  | 8 | 7 | 6 | 5 | 4 | 3 | 2  | 1   | 0 |

|----|----|----|----|----|----|----|----|-----|----|----|----|----|----|----|---|---|---|---|---|---|----|-----|---|

| 0  | 0  | 1  | 0  | 0  | Z  |    |    | AMI | 7  |    | Y  | qq | X  | qc |   | 0 | 0 | 0 | 0 |   | CC | DNI | ) |

AMF specifies the ALU or MAC operation. In this case,

AMF = 10101 for -yop operation.

AMF = 11001 for -xop operation

### 15 ALU NOT

Note that -xop is a special case of yop - xop, with yop specified to be 0.

| Z: Destina<br>Xop: X opera | tion register<br>nd |                                                                          | Y operand condition |                |

|----------------------------|---------------------|--------------------------------------------------------------------------|---------------------|----------------|

| Syntax: [ IF               | cond ] A            | $\left  \begin{array}{c} \mathbf{R} \\ \mathbf{F} \end{array} \right  =$ | NOT xop             | ;              |

| Permissible xops           | Permissible yops    | Perm                                                                     | issible conds (s    | ee Table 15.9) |

| AX0 MR2 '                  | AY0 <sup>°</sup>    | EQ                                                                       | LE                  | AC             |

| AX1 MR1                    | AY1                 | NE                                                                       | NEG                 | NOT AC         |

| AR MR0                     | AF                  | GT                                                                       | POS                 | MV             |

| SR1                        | 0                   | GE                                                                       | AV                  | NOT MV         |

| SR0                        |                     | LT                                                                       | NOT AV              | NOT CE         |

**Example:** IF NE AF = NOT AX0;

**Description:** Test the optional condition and if true, then perform the logical complement (ones complement) of the source operand and store in the destination location. If the condition is not true then perform a no-operation. Omitting the condition performs the complement operation unconditionally. The source operand is contained in the data register specified in the instruction.

### **Status Generated:**

| ASTAT: | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|--------|----|----|----|----|----|----|----|----|

|        | SS | MV | AQ | AS | AC | AV | AN | AZ |

|        | _  | _  | _  | _  | 0  | 0  | *  | *  |

- AZ Set if the result equals zero. Cleared otherwise.

- AN Set if the result is negative. Cleared otherwise.

- AV Always cleared.

- AC Always cleared.

### Instruction Format:

Conditional ALU/MAC Operation, Instruction Type 9:

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15  | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2  | 1   | 0 |  |

|----|----|----|----|----|----|----|----|-----|----|----|----|----|----|---|---|---|---|---|---|---|----|-----|---|--|

| 0  | 0  | 1  | 0  | 0  | Z  |    |    | AMI | 7  |    | Yo | qc | X  | p |   | 0 | 0 | 0 | 0 |   | CC | ONI | ) |  |

AMF specifies the ALU or MAC operation. In this case, AMF = 10100 for NOT yop operation.

## ABSOLUTE VALUE 15

AMF = 11011 for NOT xop operation.

| Z:   | Destination register | Yop:  | Y operand |

|------|----------------------|-------|-----------|

| Хор: | X operand            | CÔND: | condition |

| Syntax: [IF cond] | AR<br>AF | = ABS xop ; |

|-------------------|----------|-------------|

|-------------------|----------|-------------|

| Permi | ssible xops | Pern | Permissible conds (see Table 15 |        |  |  |  |  |  |  |  |

|-------|-------------|------|---------------------------------|--------|--|--|--|--|--|--|--|

| AX0   | MR2         | EQ   | LE                              | AC     |  |  |  |  |  |  |  |

| AX1   | MR1         | NE   | NEG                             | NOT AC |  |  |  |  |  |  |  |

| AR    | MR0         | GT   | POS                             | MV     |  |  |  |  |  |  |  |

|       | SR1         | GE   | AV                              | NOT MV |  |  |  |  |  |  |  |

|       | SR0         | LT   | NOT AV                          | NOT CE |  |  |  |  |  |  |  |

**Example:** IF NEG AF = ABS AX0;

**Description:** Test the optional condition and, if true, then take the absolute value of the source operand and store in the destination location. If the condition is not true then perform a no-operation. Omitting the condition performs the absolute value operation unconditionally. The source operand is contained in the data register specified in the instruction.

### **Status Generated:**

| ASTAT: | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|--------|----|----|----|----|----|----|----|----|

|        | SS | MV | AQ | AS | AC | AV | AN | AZ |

|        | -  | -  | -  | *  | 0  | *  | *  | *  |

- AZ Set if the result equals zero. Cleared otherwise.

- AN Set if *xop* is H#8000. Cleared otherwise.

- AV Set if  $x \circ p$  is H#8000. Cleared otherwise.

- AC Always cleared.

- AS Set if the source operand is negative. Cleared otherwise.

### Instruction Format:

Conditional ALU/MAC Operation, Instruction Type 9:

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15  | 14 | 13 | 12 | 11 | 10 | 9   | 8 | 7 | 6 | 5 | 4 | 3 | 2  | 1   | 0 |

|----|----|----|----|----|----|----|----|-----|----|----|----|----|----|-----|---|---|---|---|---|---|----|-----|---|

| 0  | 0  | 1  | 0  | 0  | Z  |    |    | AMI | 7  |    | 0  | 0  | 2  | Kob | þ | 0 | 0 | 0 | 0 |   | CC | ONI | ) |

AMF specifies the ALU or MAC operation. In this case, AMF = 11111 for ABS xop operation.

### **15** ALU INCREMENT

| Z:   | Destination register |       |           |

|------|----------------------|-------|-----------|

| Xop: | X operand            | COND: | condition |

| Syntax:                           | [IF cond]            | $\begin{vmatrix} AR \\ AF \end{vmatrix} =$         | yop + 1 ;                                                  |

|-----------------------------------|----------------------|----------------------------------------------------|------------------------------------------------------------|

| Permissible y<br>AY0<br>AY1<br>AF | EQ<br>NE<br>GT<br>GE | iissible conds<br>LE<br>NEG<br>POS<br>AV<br>NOT AV | (see Table 15.9)<br>AC<br>NOT AC<br>MV<br>NOT MV<br>NOT CE |

|                                   |                      |                                                    |                                                            |

**Example:** IF GT AF = AF + 1;

**Description:** Test the optional condition and if true, then increment the source operand by H#0001 and store in the destination location. If the condition is not true then perform a no-operation. Omitting the condition performs the increment operation unconditionally. The source operand is contained in the data register specified in the instruction.

### **Status Generated:**

| ASTAT: | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|--------|----|----|----|----|----|----|----|----|

|        | SS | MV | AQ | AS | AC | AV | AN | AZ |

|        | _  | -  | _  | -  | *  | *  | *  | *  |

|        |    |    |    |    |    |    |    |    |

| AZ | Set if the result equals zero. | Cleared otherwise. |

|----|--------------------------------|--------------------|

|    |                                |                    |

- AN Set if the result is negative. Cleared otherwise.

- AV Set if an overflow is generated. Cleared otherwise.

- AC Set if a carry is generated. Cleared otherwise.

### Instruction Format:

Conditional ALU/MAC Operation, Instruction Type 9:

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15  | 14 | 13 | 12 | 11 | 10 | 9   | 8 | 7 | б | 5 | 4 | 3 | 2  | 1   | 0 |

|----|----|----|----|----|----|----|----|-----|----|----|----|----|----|-----|---|---|---|---|---|---|----|-----|---|

| 0  | 0  | 1  | 0  | 0  | Z  |    |    | AMI | ŗ  |    | Yo | qq | 2  | Xor | ) | 0 | 0 | 0 | 0 |   | CC | ONI | ) |

AMF specifies the ALU or MAC operation. In this case,

AMF = 10001 for yop + 1 operation.

Note that the xop field is ignored for the increment operation.

## DECREMENT 15

| Z:   | Destination register | Yop:  | Y operand |

|------|----------------------|-------|-----------|

| Xop: | X operand            | CÔND: | condition |

| Syntax: | [IF cond] | AR<br>AF | = yop – 1; |

|---------|-----------|----------|------------|

|---------|-----------|----------|------------|

| Permissible yops | Permissible conds (see Table | e 15.9) |

|------------------|------------------------------|---------|

| AY0              | EQ LE                        | AC      |

| AY1              | NE NEG                       | NOT AC  |

| AF               | GT POS                       | MV      |

|                  | GE AV                        | NOT MV  |

|                  | LT NOT AV                    | NOT CE  |

|                  |                              |         |

**Example:** IF EQ AR = AY1 - 1;

**Description:** Test the optional condition and if true, then decrement the source operand by H#0001 and store in the destination location. If the condition is not true then perform a no-operation. Omitting the condition performs the decrement operation unconditionally. The source operand is contained in the data register specified in the instruction.

#### **Status Generated:**

| ASTAT: | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|--------|----|----|----|----|----|----|----|----|

|        | SS | MV | AQ | AS | AC | AV | AN | AZ |

|        | —  | —  | -  | —  | *  | *  | *  | *  |

| AZ | Set if the result equals zero. Cleared otherwise.   |

|----|-----------------------------------------------------|

| AN | Set if the result is negative. Cleared otherwise.   |

| AV | Set if an overflow is generated. Cleared otherwise. |

| AC | Set if a carry is generated. Cleared otherwise.     |

### Instruction Format:

Conditional ALU/MAC Operation, Instruction Type 9:

| 2 | 3 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15  | 14 | 13 | 12 | 11 | 10 | 9   | 8 | 7 | 6 | 5 | 4 | 3 | 2  | 1   | 0 |  |

|---|---|----|----|----|----|----|----|----|-----|----|----|----|----|----|-----|---|---|---|---|---|---|----|-----|---|--|

|   | 0 | 0  | 1  | 0  | 0  | Z  |    |    | AMI | ?  |    | Yo | p  | 2  | Kop | > | 0 | 0 | 0 | 0 |   | CC | ONI | ) |  |

AMF specifies the ALU or MAC operation. In this case,

AMF = 11000 for yop - 1 operation.

Note that the xop field is ignored for the decrement operation.

### 15 ALU DIVIDE

| Z:   | Destination register | Yop:  | Y operand |

|------|----------------------|-------|-----------|

| Хор: | X operand            | COND: | condition |

| Synta                      | <b>x:</b> 1                                   | DIVS | yop, xop;                     |

|----------------------------|-----------------------------------------------|------|-------------------------------|

|                            | 1                                             | DIVÇ | 2 xop;                        |

| Permis<br>AX0<br>AX1<br>AR | ssible xop<br>MR2<br>MR1<br>MR0<br>SR1<br>SR0 | DS   | Permissible yops<br>AY1<br>AF |

**Description:** These instructions implement **yop** ÷ **xop**. There are two divide primitives, DIVS and DIVQ. A single precision divide, with a 32-bit numerator and a 16-bit denominator, yielding a 16-bit quotient, executes in 16 cycles. Higher precision divides are also possible.

The division can be either signed or unsigned, but both the numerator and denominator must be the same; both signed or unsigned. The programmer sets up the divide by sorting the upper half of the numerator in any permissible *yop* (AY1 or AF), the lower half of the numerator in AY0, and the denominator in any permissible *xop*. The divide operation is then executed with the divide primitives, DIVS and DIVQ. Repeated execution of DIVQ implements a non-restoring conditional add-subtract division algorithm. At the conclusion of the divide operation the quotient will be in AY0.

To implement a signed divide, first execute the DIVS instruction once, which computes the sign of the quotient. Then execute the DIVQ instruction for as many times as there are bits remaining in the quotient (e.g., for a signed, single-precision divide, execute DIVS once and DIVQ 15 times).

To implement an unsigned divide, first place the upper half of the numerator in AF, then set the AQ bit to zero by manually clearing it in the Arithmetic Status Register, ASTAT. This indicates that the sign of the quotient is positive. Then execute the DIVQ instruction for as many times as there are bits in the quotient (e.g., for an unsigned single-precision divide, execute DIVQ 16 times).

## DIVIDE 15

The quotient bit generated on each execution of DIVS and DIVQ is the AQ bit which is written to the ASTAT register at the end of each cycle. The final remainder produced by this algorithm (and left over in the AF register) is not valid and must be corrected if it is needed. For more information, consult the *Division Exceptions* appendix of this manual.

#### **Status Generated:**

| ASTAT: | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|--------|----|----|----|----|----|----|----|----|

|        | SS | MV | AQ | AS | AC | AV | AN | AZ |

|        | _  | _  | *  | _  | _  | _  | _  | _  |

AQ Loaded with the bit value equal to the AQ bit computed on each cycle from execution of the DIVS or DIVQ instruction.

#### Instruction Format:

DIVQ, Instruction Type 23:

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9   | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|-----|---|---|---|---|---|---|---|---|---|

| 0  | 0  | 0  | 0  | 0  | 1  | 1  | 1  | 0  | 0  | 0  | 1  | 0  | Σ  | ζοŗ | > | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

DIVS, Instruction Type 24:

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 1 | 1 | 10 | 98 | 37 | б | 5 | 4 | 3 | 2 | 1 | 0 |

|----|----|----|----|----|----|----|----|----|----|----|------|---|----|----|----|---|---|---|---|---|---|---|

| 0  | 0  | 0  | 0  | 0  | 1  | 1  | 0  | 0  | 0  | 0  | Yop  |   | Х  | op | C  | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

### 15 ALU GENERATE ALU STATUS (ADSP-217x, ADSP-218x, ADSP-21msp58/59 only)

Xop: X operand Yop: Y o

Yop: Y operand

**Syntax:** NONE = <ALU>;

<ALU> may be any unconditional ALU operation except DIVS or DIVQ.\*

**Examples:** NONE = AX0 – AY0; NONE = PASS SR0;

**Description:** Perform the designated ALU operation, generate the ASTAT status flags, then discard the result value. This instruction allows the testing of register values without disturbing the contents of the AR or AF registers.

\* Note that the additional-constant ALU operations of the ADSP-217x, ADSP-218x, ADSP-21msp58/59 processors are also not allowed:

ADD (xop + constant) SUBTRACT X−Y (xop - constant) SUBTRACT Y−X (-xop + constant) AND, OR, XOR (xop • constant) PASS (PASS constant, using any constant other than -1, 0, or 1) TSTBIT, SETBIT, CLRBIT, TGLBIT.

### **Status Generated:**

| ASTAT: | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|--------|----|----|----|----|----|----|----|----|

|        | SS | MV | AQ | AS | AC | AV | AN | AZ |

|        | _  | _  | _  | _  | *  | *  | *  | *  |

- AZ Set if the result equals zero. Cleared otherwise.

- AN Set if the result is negative. Cleared otherwise.

- AV Set if an arithmetic overflow occurs. Cleared otherwise.

- AC Set if a carry is generated. Cleared otherwise.

### Instruction Format:

ALU/MAC operation with Data Register Move, Instruction Type 8:

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15  | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|----|----|----|----|----|----|----|-----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| 0  | 0  | 1  | 0  | 1  | 0  |    | 1  | AME |    |    | Υc | p  | Xc | p |   | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 |

|    |    |    |    |    |    |    |    |     |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

ALU codes only

## MAC 15

| Хор: Хоре                                      | erand                           |                                 | Yop:                                               | Y operai                              | nd                                                  |                                                         |

|------------------------------------------------|---------------------------------|---------------------------------|----------------------------------------------------|---------------------------------------|-----------------------------------------------------|---------------------------------------------------------|

| Syntax: []                                     | F cond]                         | M<br>M                          | $\left  \mathbf{R} \right  = \mathbf{x}\mathbf{c}$ | pp * yoj<br>xop                       | p (SS)<br>(SU)<br>(US)<br>(UU)<br>(RND              | ) ;                                                     |

| Permissible<br>MX0<br>MX1<br>MR2<br>MR1<br>MR0 | <i>xops</i><br>AR<br>SR1<br>SR0 | Permissible<br>MY0<br>MY1<br>MF | yops                                               | Permiss<br>EQ<br>NE<br>GT<br>GE<br>LT | ible conds (sea<br>LE<br>NEG<br>POS<br>AV<br>NOT AV | e Table 15.9)<br>AC<br>NOT AC<br>MV<br>NOT MV<br>NOT CE |

| Examples:                                      |                                 | 2 MR = MX<br>= SR0 * SR0        | •                                                  | UU);                                  | xop * yc<br>xop * xc                                |                                                         |

**Description:** Test the optional condition and, if true, then multiply the two source operands and store in the destination location. If the condition is not true perform a no-operation. Omitting the condition performs the multiplication unconditionally. The operands are contained in the data registers specified in the instruction. When MF is the destination operand, only bits 31-16 of the product are stored in MF.

The *xop* \* *xop* squaring operation is only available on the ADSP-217x, ADSP-218x, and ADSP-21msp58/59 processors. Both *xops* must be the same register. This option allows single-cycle X<sup>2</sup> and  $\Sigma$ X<sup>2</sup> instructions.

The data format selection field following the two operands specifies whether each respective operand is in Signed (S) or Unsigned (U) format. The *xop* is specified first and *yop* is second. If the *xop* \* *xop* operation is used, the data format selection field must be (UU), (SS), or (RND) only. There is no default; one of the data formats must be specified.

If RND (Round) is specified, the MAC multiplies the two source operands, rounds the result to the most significant 24 bits (or rounds bits 31-16 to 16 bits if there is no overflow from the multiply), and stores the result in the destination register. The two multiplication operands *xop* and *yop* (or *xop* and *xop*) are considered to be in twos complement format. All rounding is unbiased, except on the ADSP-217x, ADSP-218x, and ADSP-21msp58/59 processors, which offer a biased rounding mode. For a discussion of

(instruction continues on next page)

### 15 MAC MULTIPLY

biased vs. unbiased rounding, see "Rounding Mode" in the "Multiplier/ Accumulator" section of Chapter 2, *Computation Units*.

### **Status Generated:**

| ASTAT: | 7 | 6  | 5      | 4 | 3 | 2 | 1 | 0  |

|--------|---|----|--------|---|---|---|---|----|

|        |   | MV | $\sim$ |   |   |   |   | AZ |

|        | - | *  | _      | _ | - | - | - | _  |

MV Set on MAC overflow (if any of upper 9 bits of MR are not all one or zero). Cleared otherwise.

### **Instruction Format:**

(*xop* \* *yop*) Conditional ALU/MAC Operation, Instruction Type 9:

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16  | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2   | 1  | 0 |

|----|----|----|----|----|----|----|-----|----|----|----|----|----|----|---|---|---|---|---|---|---|-----|----|---|

| 0  | 0  | 1  | 0  | 0  | Z  |    | AMI | 7  |    |    | Yo | qc | Xc | p |   | 0 | 0 | 0 | 0 | 0 | CON | 1D |   |

AMF: Specifies the ALU or MAC Operation. In this case,

| AMF   | FUNCTION                                      | Data Format | X-Operand                              | Y-Operand    |

|-------|-----------------------------------------------|-------------|----------------------------------------|--------------|

| 00100 | xop * yop                                     | (SS)        | Signed                                 | Signed       |

| 00101 | xop * yop                                     | (SU)        | Signed                                 | Unsigned     |

| 00110 | xop * yop                                     | (US)        | Unsigned                               | Signed       |

| 00110 | xop * yop                                     | (UU)        | Unsigned                               | Unsigned     |

|       | xop * yop<br>ation register<br>erand register |             | Signed<br>perand register<br>condition | Signed<br>er |

(*xop* \* *xop*) Conditional ALU/MAC Operation, Instruction Type 9: (*ADSP*-217*x*, *ADSP*-218*x*, *ADSP*-21*msp58*/59 only)

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16  | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1   | 0 |

|----|----|----|----|----|----|----|-----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|-----|---|

| 0  | 0  | 1  | 0  | 0  | Z  |    | AMI | ?  |    |    | 0  | 0  | Xc | pp |   | 0 | 0 | 0 | 1 |   | C | ONI | ) |

AMF: Specifies the ALU or MAC Operation. In this case,

| AMF   | FUNCTION  | Data Format | X-Operand |

|-------|-----------|-------------|-----------|

| 00100 | xop * xop | (SS)        | Signed    |

| 00111 | xop * xop | (UU)        | Unsigned  |

| 00001 | xop * xop | (RND)       | Signed    |

### MULTIPLY / ACCUMULATE 15

Z: Destination register COND: condition Xop: X operand register Syntax: (SS) [IF cond] MR = MR + xop \* yop ; MF (SU) xop (US) (UU) (RND) Permissible conds (see Table 15.9) *Permissible xops Permissible yops* MX0 AR EO LE MY0 AC NEG NOT AC MX1 SR1 MY1 NE SR0 MF GT POS MR2 MV MR1 GE AV NOT MV MR0 LT NOT AV NOT CE Examples: IF GE MR = MR + MX0 \* MY1 (SS); *xop* \* *yop* MR = MR + MX0 \* MX0 (SS); xop \* xop

**Description:** Test the optional condition and, if true, then multiply the two source operands, add the product to the present contents of the MR register, and store the result in the destination location. If the condition is not true then perform a no-operation. Omitting the condition performs the multiply/accumulate unconditionally. The operands are contained in the data registers specified in the instruction. When MF is the destination operand, only bits 31-16 of the 40-bit result are stored in MF.

The *xop* \* *xop* squaring operation is only available on the ADSP-217x, ADSP-218x, and ADSP-21msp58/59 processors. Both *xops* must be the same register. This option allows single-cycle X<sup>2</sup> and  $\Sigma$ X<sup>2</sup> instructions.

The data format selection field to the right of the two operands specifies whether each respective operand is in signed (S) or unsigned (U) format. The *xop* is specified first and *yop* is second. If the *xop* \* *xop* operation is used, the data format selection field must be (UU), (SS), or (RND) only. There is no default; one of the data formats must be specified.

If RND (Round) is specified, the MAC multiplies the two source operands, adds the product to the current contents of the MR register, rounds the result to the most significant 24 bits (or rounds bits 31-16 to the nearest 16 bits if there is no overflow from the multiply/accumulate), and stores the result in the destination register. The two multiplication operands *xop* and *yop* (or *xop* and *xop*) are considered to be in twos complement format. All

## **15** MAC MULTIPLY / ACCUMULATE

rounding is unbiased, except on the ADSP-217x, ADSP-218x, and ADSP-21msp58/59 processors, which offer a biased rounding mode. For a discussion of biased vs. unbiased rounding, see "Rounding Mode" in the "Multiplier/Accumulator" section of Chapter 2, *Computation Units*.

#### **Status Generated:**

| ASTAT: | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|--------|----|----|----|----|----|----|----|----|

|        | SS | MV | AQ | AS | AC | AV | AN | AZ |

|        | -  | *  | _  | _  | _  | _  | _  | _  |

MV Set on MAC overflow (if any of upper 9 bits of MR are not all one or zero). Cleared otherwise.

#### **Instruction Format:**

(*xop* \* *yop*) Conditional ALU/MAC Operation, Instruction Type 9:

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16  | 15       | 14 | 13 | 12 | 11 | 10 | 9  | 8 | 7 | 6 | 5 | 4 | 3 | 2   | 1 | 0 |  |

|----|----|----|----|----|----|----|-----|----------|----|----|----|----|----|----|---|---|---|---|---|---|-----|---|---|--|

| 0  | 0  | 1  | 0  | 0  | Z  |    | AMI | <u>.</u> |    |    | Yo | qc | Xc | pp |   | 0 | 0 | 0 | 0 | 0 | CON | D |   |  |

AMF: Specifies the ALU or MAC Operation. In this case,

| AMF   | FUNCTION                          | Data Format              | X-Operand    | Y-Operand |

|-------|-----------------------------------|--------------------------|--------------|-----------|

| 01000 | MR+xop * yop                      | (SS)                     | Signed       | Signed    |

| 01001 | MR+xop * yop                      | (SU)                     | Signed       | Unsigned  |

| 01010 | MR+xop * yop                      | (US)                     | Unsigned     | Signed    |

| 01011 | MR+xop * yop                      | (UU)                     | Unsigned     | Unsigned  |

| 00010 | MR+xop * yop                      | (RND)                    | Signed       | Signed    |

|       | ation register<br>perand register | Yop: Y oper<br>COND: cor | and register |           |

(*xop* \* *xop*) Conditional ALU/MAC Operation, Instruction Type 9: (*ADSP-217x*, *ADSP-218x*, *ADSP-21msp58/59 only*)

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16  | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8 | 7 | 6 | 5 | 4 | 3 | 2  | 1   | 0 |

|----|----|----|----|----|----|----|-----|----|----|----|----|----|----|----|---|---|---|---|---|---|----|-----|---|

| 0  | 0  | 1  | 0  | 0  | Z  |    | AMI | 7  |    |    | 0  | 0  | Xc | pp |   | 0 | 0 | 0 | 1 |   | CC | ONE | ) |

AMF: Specifies the ALU or MAC Operation. In this case,

| AMF   | FUNCTION     | Data Format | X-Operand |

|-------|--------------|-------------|-----------|

| 01000 | MR+xop * xop | (SS)        | Signed    |

| 01011 | MR+xop * xop | (UU)        | Unsigned  |

| 00010 | MR+xop * xop | (RND)       | Signed    |

### MULTIPLY/SUBTRACT 15

| Z: Destinatio<br>Xop: X opera |           |                    | COND:     | condition      |                                       |    |

|-------------------------------|-----------|--------------------|-----------|----------------|---------------------------------------|----|

| Syntax:                       | [ IF cond | ]   MR   =<br>  MF | = MR – xo | p * yop<br>xop | (SS)<br>(SU)<br>(US)<br>(UU)<br>(RND) | ;  |

| Permissible xc                | ons Pern  | issible yops       | Permis    | sible conds (s | ee Tahle 15                           | 9) |

|                               | R MY      | 01                 | EQ        | LE             | AC                                    |    |

| MX1 S                         | R1 MY     | L                  | NĨ        | NEG            | NOT AC                                |    |

| MR2 S                         | R0 MF     |                    | GT        | POS            | MV                                    |    |

| MR1                           |           |                    | GE        | AV             | NOT MV                                | 1  |

| MR0                           |           |                    | LT        | NOT AV         | NOT CE                                |    |

| Examples:                     |           | = MR - MX          |           | U);            | хор * уор<br>хор * хор                |    |

**Description:** Test the optional condition and, if true, then multiply the two source operands, subtract the product from the present contents of the MR register, and store the result in the destination location. If the condition is not true perform a no-operation. Omitting the condition performs the multiply/subtract unconditionally. The operands are contained in the data registers specified in the instruction. When MF is the destination operand, only bits 16-31 of the 40-bit result are stored in MF.

The *xop* \* *xop* squaring operation is only available on the ADSP-217x, ADSP-218x, and ADSP-21msp58/59 processors. Both *xops* must be the same register.

The data format selection field to the right of the two operands specifies whether each respective operand is in signed (S) or unsigned (U) format. The *xop* is specified first and *yop* is second. If the *xop* \* *xop* operation is used, the data format selection field must be (UU), (SS), or (RND) only. There is no default; one of the data formats must be specified.

If RND (Round) is specified, the MAC multiplies the two source operands, subtracts the product from the current contents of the MR register, rounds the result to the most significant 24 bits (or rounds bits 31-16 to 16 bits if there is no overflow from the multiply/accumulate), and stores the result in the destination register. The two multiplication operands *xop* and *yop* (or *xop* and *xop*) are considered to be in twos complement format. All

## 15 MAC MULTIPLY/SUBTRACT

rounding is unbiased, except on the ADSP-217x, ADSP-218x, and ADSP-21msp58/59 processors, which offer a biased rounding mode. For a discussion of biased vs. unbiased rounding, see "Rounding Mode" in the "Multiplier/Accumulator" section of Chapter 2, *Computation Units*.

#### **Status Generated:**

| ASTAT: | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|--------|----|----|----|----|----|----|----|----|

|        | SS | MV | AQ | AS | AC | AV | AN | AZ |

|        | _  | *  | _  | _  | _  | _  | _  | _  |

MV Set on MAC overflow (if any of the upper 9 bits of MR are not all one or zero). Cleared otherwise.

#### **Instruction Format:**

(*xop* \* *yop*) Conditional ALU/MAC Operation, Instruction Type 9:

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16  | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2   | 1  | 0 |

|----|----|----|----|----|----|----|-----|----|----|----|----|----|----|---|---|---|---|---|---|---|-----|----|---|

| 0  | 0  | 1  | 0  | 0  | Z  |    | AMI | 7  |    |    | Yo | qq | Xo | p |   | 0 | 0 | 0 | 0 | ( | COI | ND |   |

AMF: Specifies the ALU or MAC Operation. In this case,

| AMF   | FUNCTION                          | Data Format                | X-Operand | Y-Operand |

|-------|-----------------------------------|----------------------------|-----------|-----------|

| 01100 | MR–xop * yop                      | (SS)                       | Signed    | Signed    |

| 01101 | MR–xop * yop                      | (SU)                       | Signed    | Unsigned  |

| 01110 | MR–xop * yop                      | (US)                       | Unsigned  | Signed    |

| 01111 | MR–xop * yop                      | (UU)                       | Unsigned  | Unsigned  |

| 00011 | MR–xop * yop                      | (RND)                      | Signed    | Signed    |

|       | ation register<br>perand register | Yop: Y opera<br>COND: cond |           |           |

(*xop* \* *xop*) Conditional ALU/MAC Operation, Instruction Type 9: (*ADSP-217x*, *ADSP-218x*, *ADSP-21msp58/59* only)

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16  | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8 | 7 | 6 | 5 | 4 | 3 | 2  | 1   | 0 |

|----|----|----|----|----|----|----|-----|----|----|----|----|----|----|----|---|---|---|---|---|---|----|-----|---|

| 0  | 0  | 1  | 0  | 0  | Z  |    | AMI | F  |    |    | 0  | 0  | Xc | pp |   | 0 | 0 | 0 | 1 |   | CC | DNE | ) |

AMF: Specifies the ALU or MAC Operation. In this case,

| AMF             | FUNCTION     | Data Format | X-Operand |

|-----------------|--------------|-------------|-----------|

| 01100           | MR–xop * xop | (SS)        | Signed    |

| 01111           | MR–xop * xop | (UU)        | Unsigned  |

| $0\ 0\ 0\ 1\ 1$ | MR–xop * xop | (RND)       | Signed    |

### CLEAR 15

Z: Destination register Xop: X operand register COND: condition

**Syntax:** [IF cond ]  $\begin{vmatrix} MR \\ MF \end{vmatrix} = 0$ ;

Permissible conds (see Table 15.9)

| EQ | NE     | GT  | GE     | LT     |

|----|--------|-----|--------|--------|

| LE | NEG    | POS | AV     | NOT AV |

| AC | NOT AC | MV  | NOT MV | NOT CE |

**Example:** IF GT MR = 0;

**Description:** Test the optional condition and, if true, then set the specified register to zero. If the condition is not true perform a no-operation. Omitting the condition performs the clear unconditionally. The entire 40-bit MR or 16-bit MF register is cleared to zero.

### **Status Generated:**

ASTAT: 7 6 5 4 3 2 1 0 SS MV AQ AS AC AV AN AZ - 0 - - - - - - -

MV Always cleared.

### Instruction Format:

Conditional ALU/MAC Operation, Instruction Type 9:

| 23 | 3 22 | 2 | 1 2 | 20 | 19 | 18 | 17 | 16  | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 2 1 | 0 |

|----|------|---|-----|----|----|----|----|-----|----|----|----|----|----|----|---|---|---|---|---|---|-------|---|

| C  | ) (  | ) | 1   | 0  | 0  | Z  |    | AMI | 7  |    |    | 1  | 1  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | COND  |   |

AMF: Specifies the ALU or MAC Operation. In this case, AMF = 00100 for clear operation.

## **15** MAC TRANSFER MR

Note that this instruction is a special case of xop \* yop, with yop set to zero.

Z: Destination registerCOND: conditionSyntax:[ IF cond ]MR | = MR [ (RND) ] ;MF |MF | = MR [ (RND) ] ;

Permissible conds (see Table 15.9)

| 1 01 111100 |        | 10000 10 | •••    |        |

|-------------|--------|----------|--------|--------|

| EQ          | NE     | GT       | GE     | LT     |

| LE          | NEG    | POS      | AV     | NOT AV |

| AC          | NOT AC | MV       | NOT MV | NOT CE |

**Example:** IF EQ MF = MR (RND);

**Description:** Test the optional condition and, if true, then perform the MR transfer according to the description below. If the condition is not true then perform a no-operation. Omitting the condition performs the transfer unconditionally.

This instruction actually performs a multiply/accumulate, specifying yop = 0 as a multiplicand and adding the zero product to the contents of MR. The MR register may be optionally rounded at the boundary between bits 15 and 16 of the result by specifying the RND option. If MF is specified as the destination, bits 31-16 of the result are stored in MF. If MR is the destination, the entire 40-bit result is stored in MR.

### **Status Generated:**

| ASTAT: | SS  | MV   | 5<br>AQ<br>- | AS     | AC      | AV    | AN    |                      |

|--------|-----|------|--------------|--------|---------|-------|-------|----------------------|

| MV     | Set | on M | AC ov        | erflov | v (if a | ny of | uppei | 9 bits of MR are not |

all one or zero). Cleared otherwise.

### Instruction Format:

Conditional ALU/MAC Operation, Instruction Type 9:

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16  | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2   | 1  | 0 |

|----|----|----|----|----|----|----|-----|----|----|----|----|----|----|---|---|---|---|---|---|---|-----|----|---|

| 0  | 0  | 1  | 0  | 0  | Z  |    | AMI | 7  |    |    | 1  | 1  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | ( | COI | JD |   |

AMF: Specifies the ALU or MAC Operation. In this case,

AMF = 01000 for Transfer MR operation

## CONDITIONAL MR SATURATION 15

Note that this instruction is a special case of MR + xop \* yop, with yop set to zero.

| Z:      | Destination register | COND: | condition |  |

|---------|----------------------|-------|-----------|--|

| Syntax: | IF MV SAT MR ;       |       |           |  |

**Description:** Test the MV (MAC Overflow) bit in the Arithmetic Status Register (ASTAT), and if set, then saturate the lower-order 32 bits of the 40-bit MR register; if the MV is not set then perform a no-operation.

Saturation of MR is executed with this instruction for one cycle only; MAC saturation is not a continuous mode that is enabled or disabled. The saturation instruction is intended to be used at the completion of a series of multiply/accumulate operations so that temporary overflows do not cause the accumulator to saturate.

The saturation result depends on the state of MV and on the sign of MR (the MSB of MR2). The possible results after execution of the saturation instruction are shown in the table below.

MV MSB of MR2 MR contents after saturation

| 0 | 0 | No change                               |

|---|---|-----------------------------------------|

| 0 | 1 | No change                               |

| 1 | 0 | 00000000 011111111111111111111111111111 |

| 1 | 1 | 11111111 1000000000000 0000000000000000 |

Status Generated: No status bits affected.

### Instruction Format:

Saturate MR operation, Instruction Type 25:

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| 0  | 0  | 0  | 0  | 0  | 1  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

### **15** SHIFTER ARITHMETIC SHIFT

Syntax: [IF cond] SR = [SR OR] ASHIFT xop (HI) ; (LO)

| Permiss | sible xops | Permis | sible conds (s | ee Table 15.9) |

|---------|------------|--------|----------------|----------------|

| SI      | ÁŔ         | EQ     | LE             | AC             |

| SR1     | MR2        | NE     | NEG            | NOT AC         |

| SR0     | MR1        | GT     | POS            | MV             |

|         | MR0        | GE     | AV             | NOT MV         |

|         |            | LT     | NOT AV         | NOT CE         |

**Example:** IF LT SR = SR OR ASHIFT SI (LO);

**Description:** Test the optional condition and, if true, then perform the designated arithmetic shift. If the condition is not true then perform a no-operation. Omitting the condition performs the shift unconditionally. The operation arithmetically shifts the bits of the operand by the amount and direction specified in the Shift Code from the SE register. Positive Shift Codes cause a left shift (upshift) and negative codes cause a right shift (downshift).

The shift may be referenced to the upper half of the output field (HI option) or to the lower half (LO option). The shift output may be logically ORed with the present contents of the SR register by selecting the SR OR option.

For ASHIFT with a positive Shift Code (i.e. positive value in SE), the operand is shifted left; with a negative Shift Code (i.e. negative value in SE), the operand is shifted right. The number of positions shifted is the count in the Shift Code. The 32-bit output field is sign-extended to the left (the MSB of the input is replicated to the left), and the output is zero-filled from the right. Bits shifted out of the high order bit in the 32-bit destination field (SR<sub>31</sub>) are dropped. Bits shifted out of the low order bit in the destination field (SR<sub>0</sub>) are dropped.

To shift a double precision number, the same Shift Code is used for both halves of the number. On the first cycle, the upper half of the number is shifted using an ASHIFT with the HI option; on the following cycle, the lower half of the number is shifted using an LSHIFT with the LO and OR options. This prevents sign bit extension of the lower word's MSB.

Status Generated: None affected.

## SHIFTER 15

**Instruction Format:** Conditional Shift Operation, Instruction Type 16:

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2   | 1  | 0 |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|-----|----|---|

| 0  | 0  | 0  | 0  | 1  | 1  | 1  | 0  | 0  |    | SF |    |    | Xo | p |   | 0 | 0 | 0 | 0 | 0 | CON | 1D |   |

SF Shifter Function

0100 AŚHIFT (HI)

0101

ASHIFT (HI, OR)

0110

ASHIFT (LO)

0111

ASHIFT (LO, OR)

Xop: shifter operand

COND:

condition

### 15 SHIFTER LOGICAL SHIFT

**Syntax:** [IF cond ] SR = [SR OR] LSHIFT xop | (HI) |;

| Permiss | ible xops | Permis | sible conds (s | ee Table 15.9) |

|---------|-----------|--------|----------------|----------------|

| SI      | ÁŔ        | EQ     | LE             | AC             |

| SR1     | MR2       | NE     | NEG            | NOT AC         |

| SR0     | MR1       | GT     | POS            | MV             |

|         | MR0       | GE     | AV             | NOT MV         |

|         |           | LT     | NOT AV         | NOT CE         |

**Example:** IF GE SR = LSHIFT SI (HI);

**Description:** Test the optional condition and, if true, then perform the designated logical shift. If the condition is not true then perform a no-operation. Omitting the condition performs the shift unconditionally. The operation logically shifts the bits of the operand by the amount and direction specified in the Shift Code from the SE register. Positive Shift Codes cause a left shift (upshift) and negative Codes cause a right shift (downshift).

The shift may be referenced to the upper half of the output field (HI option) or to the lower half (LO option). The shift output may be logically ORed with the present contents of the SR register by selecting the SR OR option.

For LSHIFT with a positive Shift Code, the operand is shifted left; the numbers of positions shifted is the count in the Shift Code. The 32-bit output field is zero-filled from the right. Bits shifted out of the high order bit in the 32-bit destination field ( $SR_{31}$ ) are dropped.

For LSHIFT with a negative Shift Code, the operand is shifted right; the number of positions shifted is the count in the Shift Code. The 32-bit output field is zero-filled from the left. Bits shifted out of the low order bit in the destination field (SR<sub>0</sub>) are dropped.

To shift a double precision number, the same Shift Code is used for both halves of the number. On the first cycle, the upper half of the number is shifted using the HI option; on the following cycle, the lower half of the number is shifted using the LO and OR options.

Status Generated: None affected.

## SHIFTER 15

### **Instruction Format:**

Conditional Shift Operation, Instruction Type 16:

| 23 | 3 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2   | 1  | 0 |

|----|---|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|-----|----|---|

| (  | ) | 0  | 0  | 0  | 1  | 1  | 1  | 0  | 0  |    | SF |    |    | Xc | p |   | 0 | 0 | 0 | 0 | ( | 201 | JD |   |

SF Shifter Function

Silver Function

0000

LSHIFT (HI)

0001

LSHIFT (HI, OR)

0010

LSHIFT (LO)

0011

LSHIFT (LO, OR)

Xop: shifter operand

condition COND:

# **15** SHIFTER NORMALIZE

Syntax: [IF cond] SR = [SR OR] NORM xop (HI) (LO)

| Permiss | sible xops | Permis | sible conds (s | ee Table 15.9) |

|---------|------------|--------|----------------|----------------|

| SI      | ÁŔ         | EQ     | LE             | AC             |

| SR1     | MR2        | NE     | NEG            | NOT AC         |

| SR0     | MR1        | GT     | POS            | MV             |

|         | MR0        | GE     | AV             | NOT MV         |

|         |            | LT     | NOT AV         | NOT CE         |

**Example:** SR = NORM SI (HI) ;

**Description:** Test the optional condition and, if true, then perform the designated normalization. If the condition is not true then perform a no-operation. Omitting the condition performs the normalize unconditionally. The operation arithmetically shifts the input operand to eliminate all but one of the sign bits. The amount of the shift comes from the SE register. The SE register may be loaded with the proper Shift Code to eliminate the redundant sign bits by using the Derive Exponent instruction; the Shift Code loaded will be the negative of the quantity: (the number of sign bits minus one).

The shift may be referenced to the upper half of the output field (HI option) or to the lower half (LO option). The shift output may be logically ORed with the present contents of the SR register by selecting the SR OR option. When the LO reference is selected, the 32-bit output field is zero-filled to the left. Bits shifted out of the high order bit in the 32-bit destination field (SR<sub>31</sub>) are dropped.

The 32-bit output field is zero-filled from the right. If the exponent of an overflowed ALU result was derived with the HIX modifier, the 32-bit output field is filled from left with the ALU Carry (AC) bit in the Arithmetic Status Register (ASTAT) during a NORM (HI) operation. In this case (SE=1 from the exponent detection on the overflowed ALU value) a downshift occurs.

To normalize a double precision number, the same Shift Code is used for both halves of the number. On the first cycle, the upper half of the number is shifted using the HI option; on the following cycle, the lower half of the number is shifted using the LO and OR options.

Status Generated: None affected.

## SHIFTER 15

### **Instruction Format:**

Conditional Shift Operation, Instruction Type 16:

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 2 1 | 0 |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|-------|---|

| 0  | 0  | 0  | 0  | 1  | 1  | 1  | 0  | 0  |    | SF |    |    | Xo | p |   | 0 | 0 | 0 | 0 | COND  |   |

SF Shifter Function

1000

NORM (HI) NORM (HI, OR) NORM (LO)  $1\,0\,0\,1$

1010

1011 NORM (LO, OR)

Xop: shifter operand

COND: condition

### **15** SHIFTER DERIVE EXPONENT

| Syntax:       | [IF cond] SE = EXP | хор          | (HI);<br>(LO);<br>(HIX); |

|---------------|--------------------|--------------|--------------------------|

| Dormissihlo v | Dorne Dorne        | vicciple con | ide (coo Tablo 1         |

| Permissi | ble xops | Permissible conds (see Table 15. |        |        |  |  |  |  |  |

|----------|----------|----------------------------------|--------|--------|--|--|--|--|--|

| SI       | AR       | EQ                               | LE     | AC     |  |  |  |  |  |

| SR1      | MR2      | NE                               | NEG    | NOT AC |  |  |  |  |  |

| SR0      | MR1      | GT                               | POS    | MV     |  |  |  |  |  |

|          | MR0      | GE                               | AV     | NOT MV |  |  |  |  |  |

|          |          | LT                               | NOT AV | NOT CE |  |  |  |  |  |

**Example:** IF GT SE = EXP MR1 (HI) ;

**Description:** Test the optional condition and, if true, perform the designated exponent operation. If the condition is not true then perform a no-operation. Omitting the condition performs the exponent operation unconditionally.

The EXP operation derives the effective exponent of the input operand to prepare for the normalization operation (NORM). EXP supplies the source operand to the exponent detector, which generates a Shift Code from the number of leading sign bits in the input operand. The Shift Code, stored in SE at the completion of the EXP instruction, is the effective exponent of the input value. The Shift Code depends on which exponent detector mode is used (HI, HIX, LO).

In the HI mode, the input is interpreted as a single precision signed number, or as the upper half of a double precision signed number. The exponent detector counts the number of leading sign bits in the source operand and stores the resulting Shift Code in SE. The Shift Code will equal the negative of the number of redundant sign bits in the input.

In the HIX mode, the input is interpreted as the result of an add or subtract which may have overflowed. HIX is intended to handle shifting and normalization of results from ALU operations. The HIX mode examines the ALU Overflow bit (AV) in the Arithmetic Status Register: if AV is set, then the effective exponent of the input is +1 (indicating that an ALU overflow occurred before the EXP operation), and +1 is stored in SE. If AV is not set, then HIX performs exactly the same operations as the HI mode.

# SHIFTER 15

In the LO mode, the input is interpreted as the lower half of a double precision number. In performing the EXP operation on a double precision number, the higher half of the number must first be processed with EXP in the HI or HIX mode, and then the lower half can be processed with EXP in the LO mode. If the upper half contained a non-sign bit, then the correct Shift Code was generated in the HI or HIX operation and that is the code that is stored in SE. If, however, the upper half was all sign bits, then EXP in the LO mode totals the number of leading sign bits in the double precision word and stores the resulting Shift Code in SE.

### **Status Generated:**

| ASTAT: |    | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|--------|----|----|----|----|----|----|----|----|

|        | SS | MV | AQ | AS | AC | AV | AN | AZ |

|        | *  | _  | _  | _  | _  | _  | _  | -  |

SS

Set by the MSB of the input for an EXP operation in the HI or HIX mode with AV = 0. Set by the MSB inverted in the HIX mode with AV = 1. Not affected by operations in the LO mode.

### **Instruction Format:**

Conditional Shift Operation, Instruction Type 16:

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2   | 1  | 0 |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|-----|----|---|

| 0  | 0  | 0  | 0  | 1  | 1  | 1  | 0  | 0  |    | SF |    |    | Xc | р |   | 0 | 0 | 0 | 0 | ( | COI | ND |   |

SF Shifter Function

1100 EXP (HI) 1101 EXP (HIX) 1110 EXP (LO)

Xop: shifter operand

COND: condition

## **15** SHIFTER BLOCK EXPONENT ADJUST

### **Syntax:** [IF cond ] SB = EXPADJ xop ;

| Permissi | ble xops | Permis | sible conds (see | Table 15.9) |

|----------|----------|--------|------------------|-------------|

| SI       | AR       | EQ     | LE               | AC          |

| SR1      | MR2      | NE     | NEG              | NOT AC      |

| SR0      | MR1      | GT     | POS              | MV          |

|          | MR0      | GE     | AV               | NOT MV      |

|          |          | LT     | NOT AV           | NOT CE      |

**Example:** IF GT SB = EXPADJ SI ;